# БИБЛИОТЕКА КРЕМНИЕВЫХ КМОП СВЧ-ЭЛЕМЕНТОВ И СЛОЖНО-ФУНКЦИОНАЛЬНЫХ БЛОКОВ ДЛЯ ПОСТРОЕНИЯ ПРИЕМО-ПЕРЕДАЮЩИХ МОДУЛЕЙ

## LIBRARY OF SILICON CMOS MICROWAVE DEVICES AND COMPLEX FUNCTION BLOCKS FOR TRANSCEIVER MODULES

УДК 621.382

Д.Андреев\*, Д.Атамась\*, Д.Копцев\*, О.Ковалева\*

D.Andreev\*, D.Atamas\*, D.Koptsev\*, O.Kovaleva\*

**Разработана библиотека СВЧ-элементов и сложно-функциональных блоков, позволяющая корректно моделировать электрические характеристики СВЧ-транзисторов на частотах до 12 ГГц. Показан набор сложно-функциональных блоков, полученных с использованием указанных моделей.**

A library of microwave components and complex function blocks for correct simulation of the electrical properties of microwave transistors at frequencies up to 12 GHz is developed. A set of complex function blocks obtained using these models is presented.

**С**оздание многофункциональных однокристальных СБИС позволяет значительно улучшать массогабаритные характеристики конечного изделия, снижать стоимость, повышать надежность и стабильность процесса

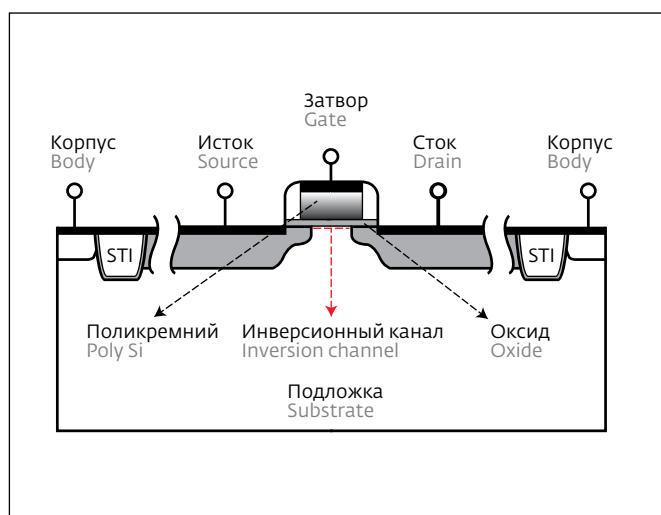

Рис.1. Структура МОП-транзистора

Fig.1. Structure of the MOS transistor

изготовления. Актуальной задачей является разработка монокристалльных приемо-передающих устройств СВЧ-диапазона. Обычно для изготовления отдельных блоков высокочастотного тракта используют МИС, полученные с применением соединений  $A^3B^5$ , наиболее часто – GaAs и GaN. Существенными недостатками данных технологий является высокая стоимость изделий и сравнительно низкий процент выхода годных. По этим причинам изготовление больших СБИС по данным технологиям не целесообразно, особенно для коммерческого применения.

До недавнего времени кремниевые технологии, хорошо зарекомендовавшие себя в производстве цифровых и цифро-аналоговых СБИС [1], не позволяли добиться требуемых значений СВЧ-характеристик, в частности, коэффициента усиления и шума. С развитием кремниевых технологий и уменьшением проектных норм до 180 нм и ниже появилась возможность изготавливать кремниевые СВЧ МИС с необходимыми СВЧ-характеристиками. Несмотря на то что кремниевые СВЧ МИС по-прежнему уступают по значениям параметров компонентам, выполненным на  $A^3B^5$ , возможность интеграции цифровой и СВЧ-

\* АО "Научно-исследовательский институт молекуллярной электроники" / Research institute for molecular electronics (MERI).

частей на один кристалл делает актуальной разработку СВЧ-устройств по кремниевым технологиям.

Разработка СБИС – сложная задача, для решения которой требуются большие затраты времени и ресурсов. В ряде случаев для получения необходимых характеристик требуется несколько производственных итераций. Для снижения времени и затрат на проектирование, а также сокращение числа производственных итераций, необходимо использование специальных библиотек, содержащих поведенческие модели всех элементов. Еще более эффективным является применение библиотек сложно-функциональных блоков (СФБ), представляющих собой топологию некоторого функционального узла с известными характеристиками.

### СВЧ-МОДЕЛИ МОП-ТРАНЗИСТОРОВ

Типовая структура МОП-транзистора приведена на рис.1 [2]. Для СВЧ-применений одним из важнейших параметров транзистора является граничная частота  $f_t$ . Согласно [2] она определяется как частота, при которой малосигнальный коэффициент усиления по току  $H_{21}$  равен единице (0 дБ). Для технологий уровня 180 нм типичные значения граничной частоты n-МОП-транзисторов составляют около 30–40 ГГц, а типичные значения граничной частоты p-МОП-транзисторов

составляют 15–20 ГГц. При выборе технологии, обеспечивающей надежное функционирование схемы, используется правило, согласно которому граничная частота транзистора должна быть не менее чем в 10 раз выше, чем рабочая частота микросхемы [2]. Таким образом, технология КМОП 180 нм может успешно применяться для построения схем с рабочими частотами до 3–4 ГГц. Однако в ряде применений возможно построение схем, рабочая частота которых в 4–5 раз ниже граничной частоты транзистора. Это наиболее актуально для схем, построенных на переключателях сигналов.

Другими важными характеристиками МОП-транзистора являются: максимальная частота осцилляции  $f_{max}$ , то есть частота, на которой коэффициент усиления по мощности равен единице; минимальный коэффициент шума  $NF_{min}$ ; точка интермодуляции напряжения третьего порядка  $V_{ip3}$ ; тепловой шум  $i_d^2$ .

Ниже приведены формулы, позволяющие рассчитать эти параметры [3, 4]:

$$f_t = \frac{1}{2\pi} \frac{g_m}{C_{gg} + C_{par} + C_{gso} + C_{gdo}}$$

$$f_{max} = \frac{1}{2\sqrt{(R_g + R_i)(g_{ds} + 2\pi f_t C_{gdo})}}$$

The creation of a multifunctional single-chip very large scale IC can significantly improve weight and size characteristics of the final product, reduce the cost, improve the reliability and stability of the manufacturing process. An actual task is the development of single-chip UHF transceivers. Usually for the manufacture of separate blocks of high-frequency tract MMIC obtained with the use of A<sup>3</sup>B<sup>5</sup> compounds, the most common GaAs and GaN.

Generally for production of separate blocks of a high-frequency path small ICs are used, which are made with the use of A<sup>3</sup>B<sup>5</sup> compounds, the most common – of GaAs and GaN. Major limitations of these technologies are the high

cost of goods and a relatively low percentage yield. For these reasons, the use of these technologies in manufacturing of very large scale ICs is not appropriate, especially for commercial ICs.

Until recently, silicon technology, which is well proven in the production of digital and mixed-signal very large scale IC [1], does not allow to achieve the required microwave characteristics, in particular, of amplification and noise figure. With the development of silicon technology and the reduction of the feature sizes to 180 nm and below, it became possible to manufacture silicon MMIC with the desired microwave characteristics. Despite the fact that the parameters of the silicon MMIC are still worse than that of

components based on A<sup>3</sup>B<sup>5</sup>, integration of digital and microwave parts on a single crystal makes relevant the development of microwave devices with use of silicon technology.

The development of very large scale ICs is a complex task, requiring large expenditures of time and resources. In some cases, obtaining the required characteristics requires several production iterations. To reduce the time and costs of design, as well as the number of production iterations, it is necessary to use a special library containing the behavioral models of all elements. Even more effective is the use of the library of complex function blocks (CFB), which represent the topology of some functional part with known characteristics.

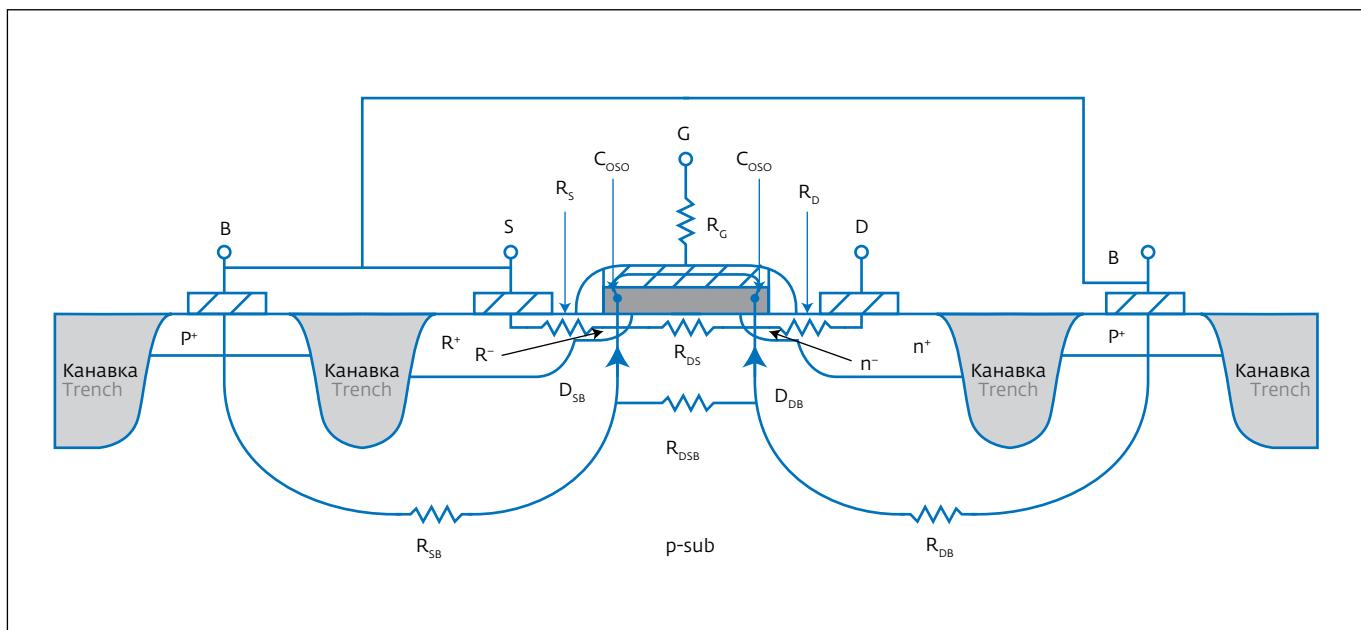

Рис.2. Поперечное сечение транзистора с указанием паразитных компонентов

Fig.2. Cross section of the transistor with the parasitic components

$$NF_{min} = 1 + K \frac{f}{f_t} \sqrt{g_m (R_g + R_i + R_s)}$$

$$V_{ip3} = \sqrt{\frac{24g_m''}{g_m}}$$

$$\overline{i_d^2} = 4KT\gamma g_{d0} \Delta f$$

где К – постоянная Больцмана;  $g_m$  – проводимость;  $g_m''$  – вторая производная проводимости;  $C_{gg}$ ,  $C_{par}$ ,  $C_{gso}$  и  $C_{gdo}$  – входная емкость, паразитная емкость затвор-подложка и емкости переходов сток-затвор и исток-затвор;  $R_g$  и  $R_i$  – сопротивление затвора и реальная часть входного импеданса за счет не квазистатических эффектов соответственно;  $R_s$  – сопротивление истока.

Обычно в стандартные поставки комплекса средств проектирования включены модели элементной базы, разработанные для цифрового и низкочастотного аналогового проектирования. Однако обычно эти модели некорректно описывают поведение приборов на высоких частотах, так как не учитывают все эффекты. Показанный на рис.2 четырехпортовый МОП-транзистор можно разделить на две части: внутренний и внешний транзистор.

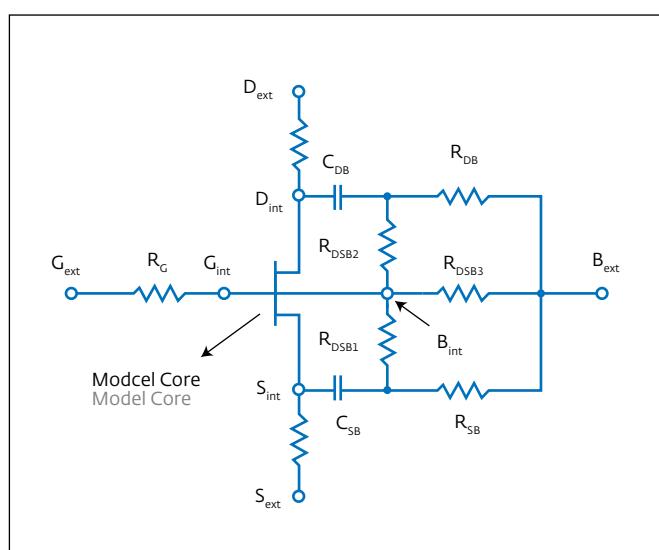

Внешний транзистор содержит такие компоненты, как сопротивление затвора  $R_s$ , емкости перекрытия затвор-сток  $C_{gso}$  и затвор-исток  $C_{gdo}$  и другие, которые не учитывает цифровая модель транзистора. На рис.3 показан пример СВЧ-модели транзистора [5].

При разработке СВЧ-модели в данной работе за основу взята модель BSIM4SOI4 и к ней добавлены внешние компоненты, учитывающие эффекты, возникающие на высоких частотах.

Рис.3. Пример СВЧ МОП-транзистора на основе цифровой модели

Fig.3. An example of a microwave MOS transistor based on a digital model

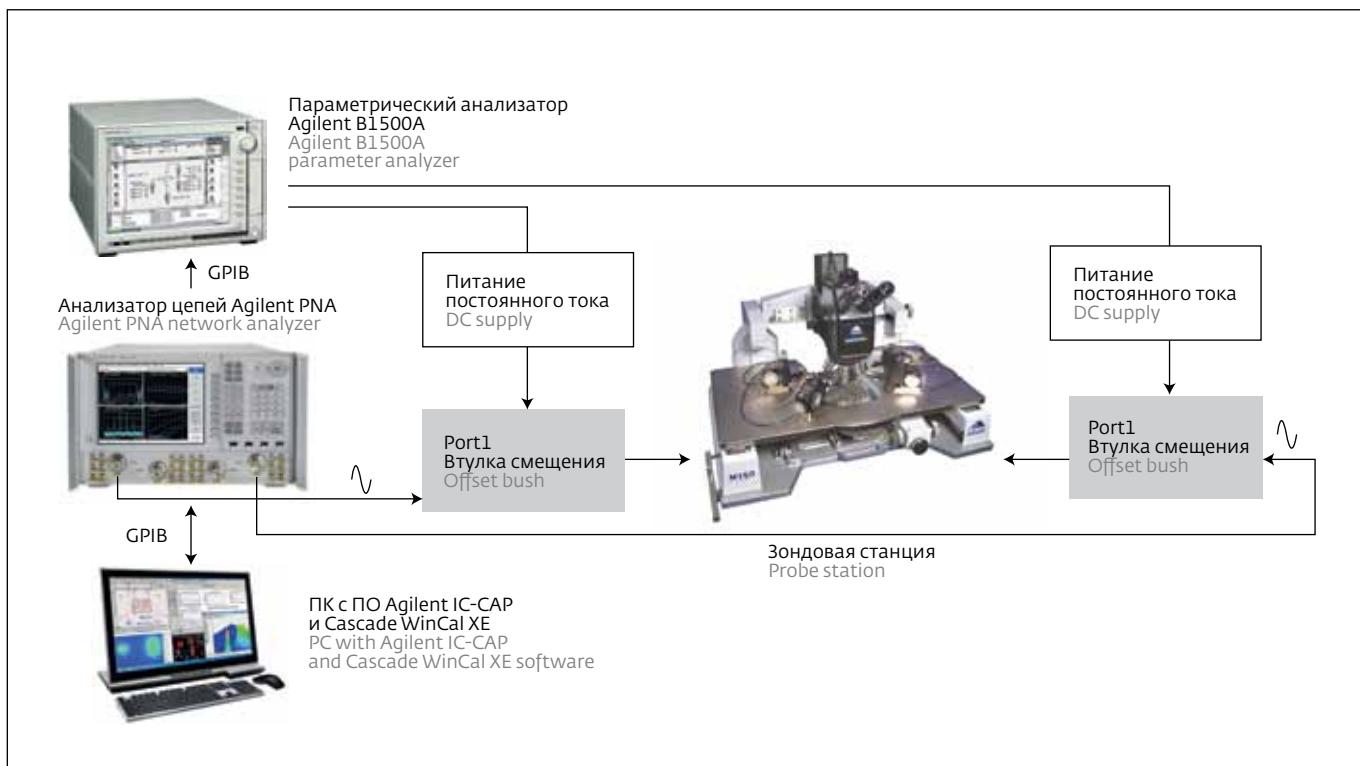

Рис.4. Блок-схема измерительного комплекса

Fig.4. Block diagram of the measuring complex

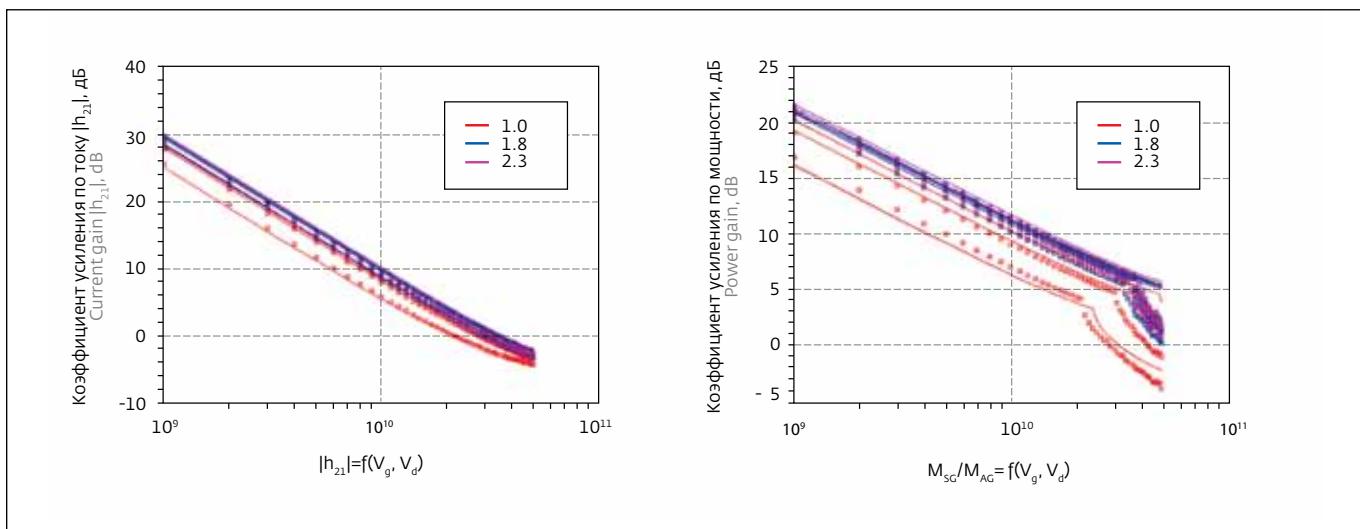

так. Измерения тестового кристалла были выполнены с помощью программно-аппаратного комплекса, показанного на рис.4. На рис.5 приведено сравнение результатов работы модели и данных измерений.

### НАБОР СЛОЖНО-ФУНКЦИОНАЛЬНЫХ БЛОКОВ ДЛЯ СОЗДАНИЯ БЕСПРОВОДНЫХ ПРИЕМО-ПЕРЕДАЮЩИХ УСТРОЙСТВ

Набор блоков, который планируется включить в состав библиотеки СФБ, приведен в табл.1.

### MICROWAVE MODEL OF MOS TRANSISTORS

The typical structure of the MOS transistor is shown in Fig.1 [2]. For microwave applications, the transistor cutoff frequency  $f_t$  is one of the most important parameters. According to [2] it is defined as the frequency at which the small-signal current amplification factor  $H_{21}$  is equal to one (0 dB). For 180 nm technology the typical values of the cutoff frequency of nMOS transistors are about of 30–40 GHz, and the typical values of the cutoff frequency of pMOS transistors are from 15 to 20 GHz. When choosing technology that

ensures reliable operation of the circuit, the rule is used according to which the cutoff frequency of the transistor should be not less than 10 times higher than the chip speed [2]. Thus, the 180 nm CMOS technology can be successfully used to create circuits with chip speed up to 3–4 GHz. However, in some applications it is possible to build circuits, which speed is 4–5 times below the cutoff frequency of the transistor. This is especially important for circuits, based on the signal selector.

Other important characteristics of a MOS transistor are: maximum oscillation frequency  $f_{max}$ , i.e. the frequency at which the

amplification is equal to 1; minimum noise figure  $NF_{min}$ ; third-order intermodulation point  $V_{ip3}$ ; thermal noise  $i_d^2$ . Below are formulas to calculate these parameters [3, 4]:

$$f_t = \frac{1}{2\pi} \frac{g_m}{C_{gg} + C_{par} + C_{gso} + C_{gdo}}$$

$$f_{max} = \frac{1}{2\sqrt{(R_g + R_i)(g_{ds} + 2\pi f_t C_{gdo})}}$$

$$NF_{min} = 1 + K \frac{f}{f_t} \sqrt{g_m (R_g + R_i + R_s)}$$

$$V_{ip3} = \sqrt{\frac{24g_m}{g_m''}}$$

Таблица 1. Набор сложно-функциональных блоков

Table 1. Set of complex function blocks

| № | Функциональное назначение<br>Functional purpose | Диапазон частот, ГГц<br>Frequency range, GHz |

|---|-------------------------------------------------|----------------------------------------------|

| 1 | Малошумящий усилитель<br>Low-noise amplifier    | 0,5–2                                        |

| 2 | SPDT-переключатель<br>SPDT switch               | 8–12                                         |

| 3 | SPDT-переключатель<br>SPDT switch               | 4–8                                          |

| 4 | SPDT-переключатель<br>SPDT switch               | 2–4                                          |

| 5 | SPDT-переключатель<br>SPDT switch               | 1–2                                          |

| 6 | Аттенюатор<br>Attenuator                        | 8–12                                         |

| 7 | Фазовращатель<br>Phase changer                  | 9,5–10,5                                     |

Все блоки изготавливаются по отечественной технологии КМОП КНИ 180 нм на предприятии ОАО "НИИМЭ и Микрон" по стандартному серийному технологическому процессу, что гарантирует высокий процент выхода годных, надежность и качество продукции. Измерения проводились с помощью специального программно-аппаратного комплекса на основе оборудования фирмы Agilent.

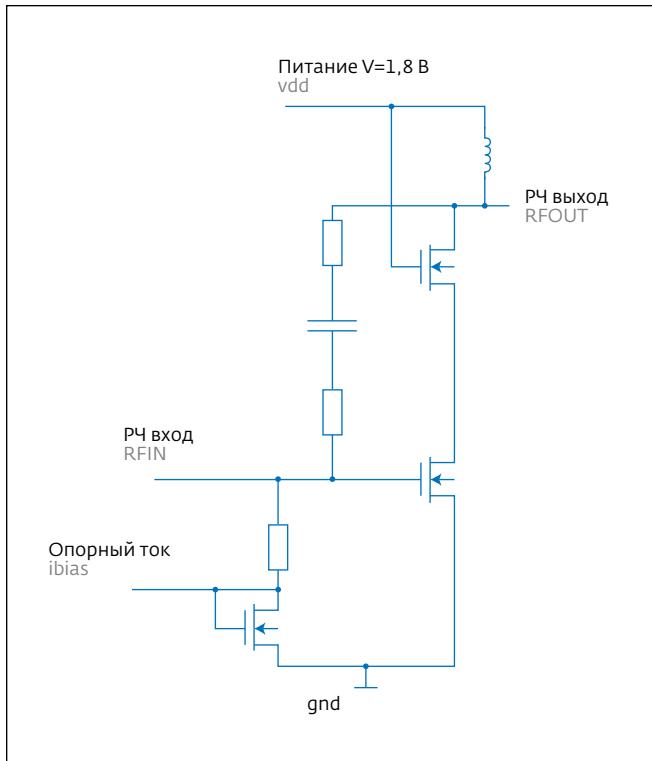

Малошумящий усилитель (МШУ) – один из ключевых блоков в приемном СВЧ-тракте систем радиосвязи, радиолокации и навигации. Его задача – увеличить малый сигнал до требуемого уровня, внеся при этом минимальный шум. Разработанный МШУ построен по однокаскодной схеме на n-МОП-транзисторах (рис.6).

При создании современных многоканальных СВЧ-устройств необходимо решать задачи ком-

Таблица 2. Расчетные технические характеристики малошумящего усилителя в сравнении с аналогами

Table 2. Design parameters of low-noise amplifier in comparison with analogues

| Параметр<br>Parameter                   | [7]                            | [8]                                | [9]         | [10]                           | НИИМЭ и Микрон<br>MERI and Mikron |

|-----------------------------------------|--------------------------------|------------------------------------|-------------|--------------------------------|-----------------------------------|

| Технология<br>Technology                | КМОП, 0,18 мкм<br>0.18 μm CMOS | БиКМОП, 0,13 мкм<br>0.13 μm BiCMOS | GaAs, рНЕМТ | КМОП, 0,18 мкм<br>0.18 μm CMOS | КНИ, 0,18 мкм<br>0.18 μm SOI      |

| Частота, ГГц<br>Frequency, GHz          | 0,4–5                          | 3–5                                | 3–5         | 5–6                            | 0,5–3                             |

| Коэф. усиления, дБ<br>Amplification, dB | 16,5–10                        | 21–20                              | ≥20         | 20                             | 12                                |

| Коэф. шума, дБ<br>Noise figure, dB      | 3,3                            | 2,4                                | 3           | 0,8                            | 4,2                               |

$$\overline{i_d^2} = 4KTg_{d0}\Delta f$$

where K is Boltzmann constant;  $g_m$  is conductivity;  $g_m''$  is the second derivative of the conductivity;  $C_{gg}$ ,  $C_{par}$ ,  $C_{gso}$  and  $C_{gdo}$  are input capacitance, parasitic capacitance of the gate-substrate and junction capacitances for drain-gate and source-gate;  $R_g$  and  $R_i$  are gate resistance and the real part of the input impedance due to non quasi-static effects, respectively;  $R_s$  is source resistance.

Usually standard set of design tools include models of the circuitry developed for digital and low frequency analog design. However, typically these models incorrectly

describe the behavior of devices at high frequencies, as it does not take into account all the effects. Shown in Fig.2 four-port MOS transistor can be divided into two parts: the internal and the external transistor. External transistor contains such components as a shutter resistance  $R_s$ , gate-to-drain overlap capacitance  $C_{gdo}$ , gate-to-source overlap capacitance  $C_{gso}$  and others, which does not take into account the digital model of the transistor. Fig.3 shows an example of a microwave transistor model [5].

The development of microwave model in this paper is based on the BSIM4SOI4 model with added

external components, which take into account the effects at high frequencies. The test chip was measured using a hardware-software complex (Fig.4). Fig.5 compares the results of modelling and measurement.

### SET OF COMPLEX FUNCTION BLOCKS FOR CREATION OF WIRELESS TRANSCEIVER

Table 1 shows a set of blocks which is planned to be included in the CFB library. All blocks are manufactured by domestic 180 nm CMOS SOI technology at MERI and Mikron JSC in the standard production process that guarantees high yield rate,

Рис.5. Измеренные и промоделированные значения параметров транзисторов

Fig.5. Measured and simulated values of parameters of transistors

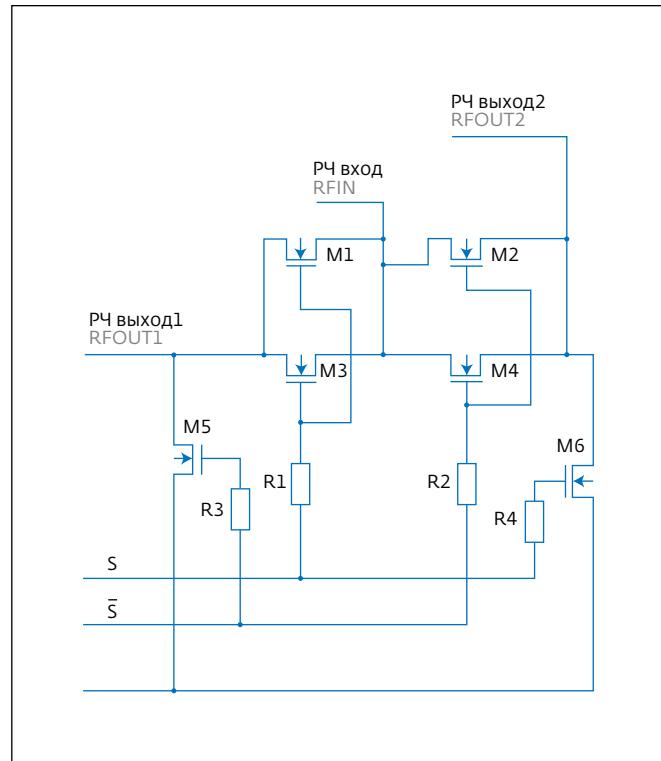

мутации СВЧ-сигналов между каналами. Для этого требуются СВЧ-переключатели, позволяющие коммутировать СВЧ-сигналы так, чтобы не происходило ограничений по рабочим частотам, скорости переключения, мощности.

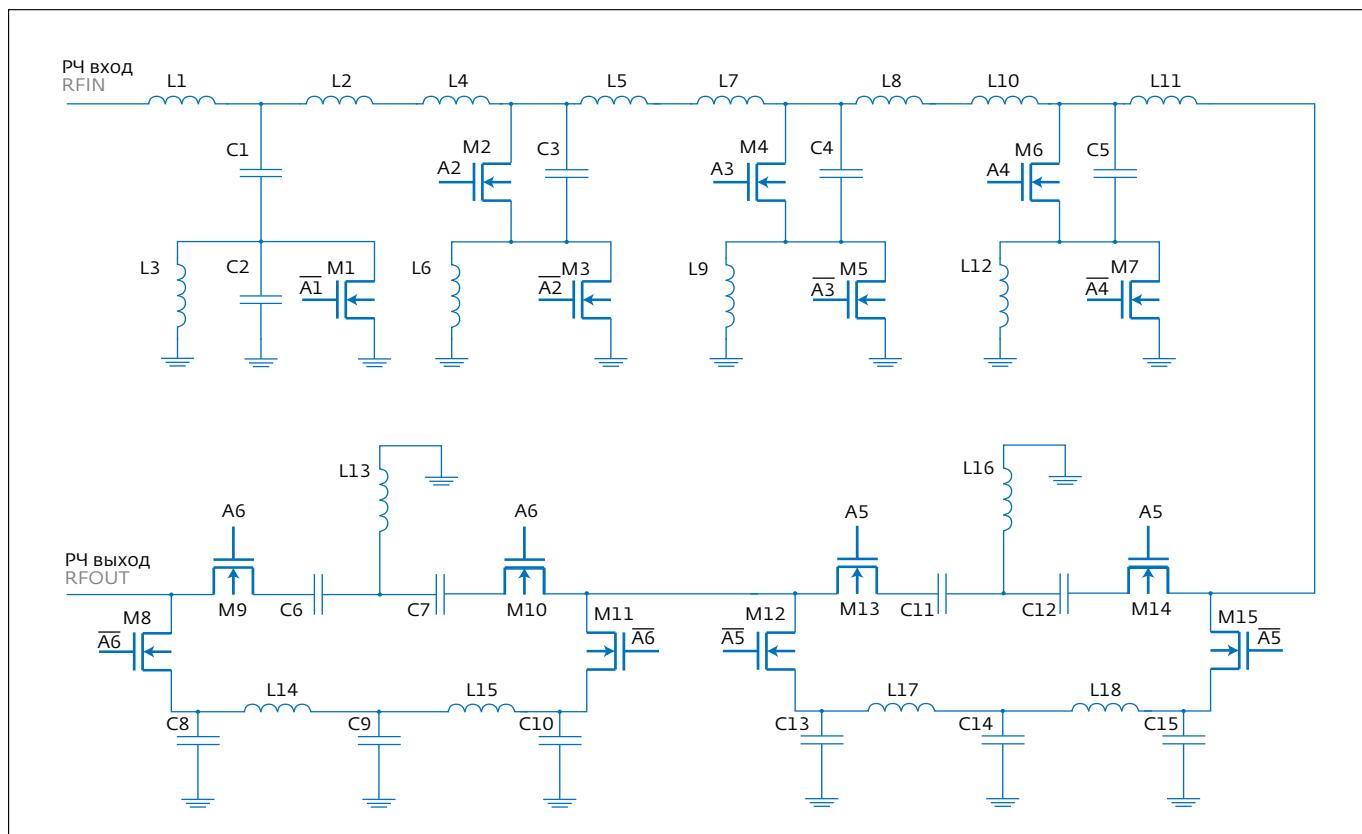

Переключатели сигналов построены по схеме, приведенной на рис.7. В зависимости от требуе-

мого частотного диапазона индивидуально подбираются оптимальные значения ширин проходного и шунтирующего транзисторов. Задача данной оптимизации – получение минимального уровня вносимых потерь во включенном состоянии при обеспечении достаточного уровня развязки в выключенном состоянии.

Рис.6. Электрическая схема СФБ МШУ

Fig.6. Circuit diagram for CFB LNA

Рис.7. Электрическая схема SPDT-ключа

Fig.7. Circuit diagram for SPDT switch

Таблица 3. Расчетные технические характеристики SPDT-переключателей в сравнении с аналогами

Table 3. Design parameters of SPDT switch in comparison with analogues

| Параметр<br>Parameter                                                   | НИИМЭ и Микрон<br>MERI and Mikron     |     |     |      | [11]       | [12]                                        |

|-------------------------------------------------------------------------|---------------------------------------|-----|-----|------|------------|---------------------------------------------|

|                                                                         | 1                                     | 2   | 3   | 4    |            |                                             |

| Технология<br>Technology                                                | КМОП КНИ 0,18 мкм<br>0.18 μm CMOS SOI |     |     |      | КНИ<br>SOI | КМОП КНИ<br>0,25 мкм<br>0.25 μm CMOS<br>SOI |

| Диапазон частот, ГГц<br>Frequency range, GHz                            | 1–2                                   | 2–4 | 4–8 | 8–12 | 0,9        | 2,4–5                                       |

| Уровень вносимых потерь, дБ<br>Level of insertion loss, dB              | 1                                     | 1,6 | 2,2 | 3    | 0,39       | 1                                           |

| Развязка в выключенном состоянии, дБ<br>Decoupling in the off state, dB | >30                                   | >30 | >30 | >25  | 49         | 46                                          |

| Размер кристалла, мм <sup>2</sup><br>Chip size, mm <sup>2</sup>         | 0,1×0,15 (без КП)                     |     |     |      | –          | –                                           |

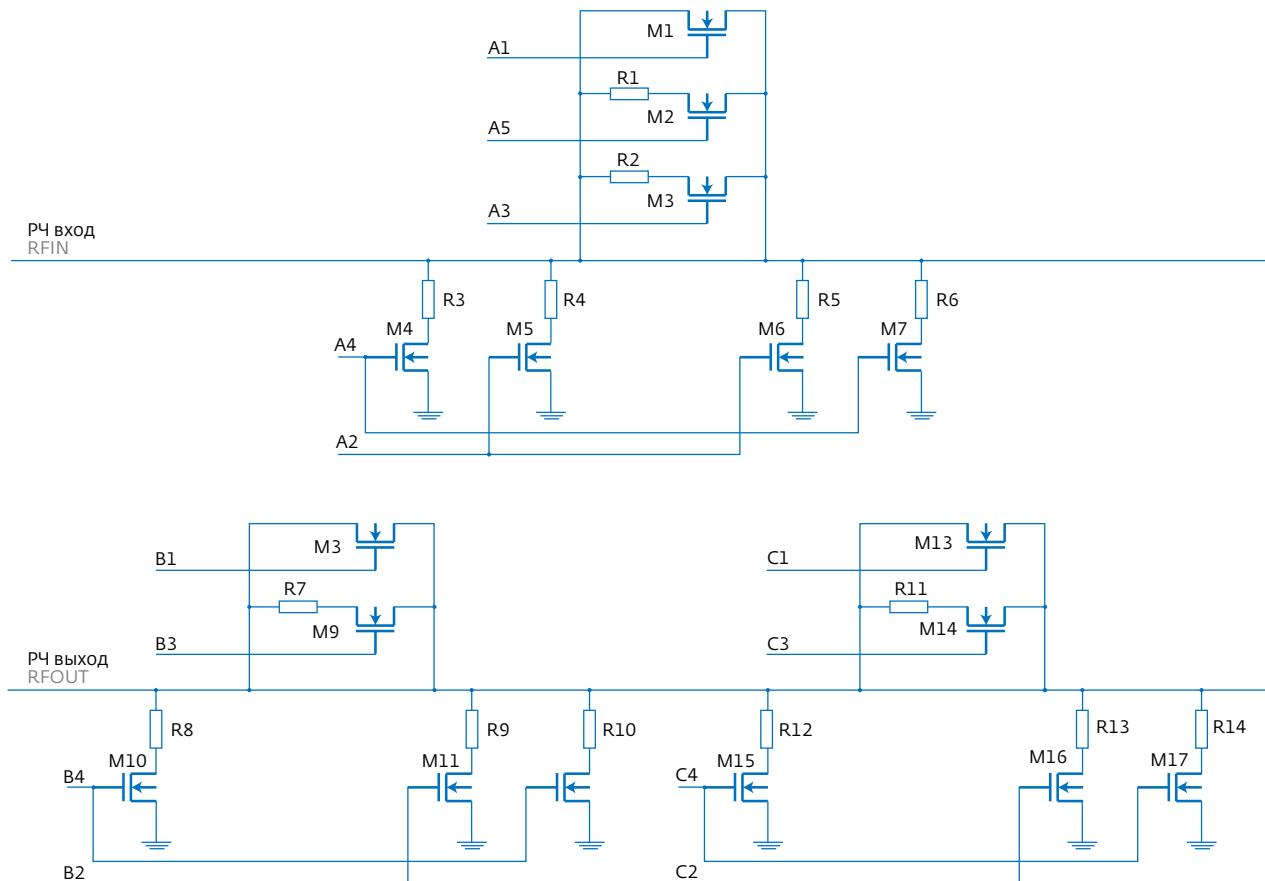

Цифровые аттенюаторы находят широкое применение во многих современных системах связи, позволяя регулировать ослабление с определенным фиксированным шагом. Обычно цифровой аттенюатор представляет собой набор резистивных аттенюаторов П- или Т-типа, разделенных переключателями сигналов, которые позволяют пропускать сигнал через резистивный аттенюатор или в обход его с минимальным уровнем вносимых потерь [13]. В таком случае уровень вносимых потерь определяется следующей формулой:

reliability and product quality. The measurements were carried out with the help of special hardware-software complex on the basis of Agilent equipment.

Low-noise amplifier (LNA) is one of the key blocks in the microwave receiving path of telecommunication, radar and navigation systems. Its mission is to increase small signal to the required level, making the minimum noise. Designed LNA is built using single-section layout on n-MOS transistors (Fig.6).

When creating a modern multi-channel microwave devices it is necessary to solve the problem of switching microwave signals between the

channels. This requires microwave switches, which allows switching the microwave signals so that there were no restrictions on operating frequency, switching speed, power.

Signal switches are constructed according to the scheme shown in Fig.7. Depending on the desired frequency band the optimum values of the widths of the feed-through and bypassing transistors are individually selected. The objective of this optimization is the achievement of a minimal level of insertion loss in the on state with sufficient level of isolation in the off state.

Digital attenuators are widely used in many modern

$$L_{\text{ат}} = 2NL_{\text{пер}} + NL_{\text{проход}}$$

где N – разрядность аттенюатора,  $L_{\text{пер}}$  – потери, вносимые одним переключателем,  $L_{\text{проход}}$  – потери, вносимые проходными каналами выключенных аттенюирующих ячеек. В связи с этим при разработке аттенюатора применена схема на основе предложенной в работе [13], которая основана на включении переключателей в состав ячейки и объединении двух секций в один блок. На рис.8 приведена электрическая схема аттенюатора,

communication systems, allowing to adjust the attenuation with a fixed step. Typically, the digital attenuator is a set of resistive attenuators of P- or T-type, separated by a signal switches that allows to pass the signal through a resistive attenuator, or bypassing it with minimal insertion loss [13]. In this case, the level of insertion loss is determined by the following formula:

$$L_{\text{ат}} = 2NL_{\text{пер}} + NL_{\text{проход}}$$

where N is the attenuator capacity,  $L_{\text{пер}}$  is loss in one switch,  $L_{\text{проход}}$  is loss of insertion-through channels of switched off attenuator cells. In

Рис.8. Электрическая схема цифрового аттенюатора

Fig.8. Circuit diagram for digital attenuator

this regard the attenuator scheme based on the proposed in [13], which is based on the inclusion of switches in the cells and blocking of the two sections, is used. Fig.8 shows the circuit diagram of the attenuator, and Fig.9 – topology of the chip for experimental studies of two designs of the attenuator with different management interface and SPDT switch optimized for a frequency range of 8-12 GHz.

Microwave phase changers are most common used in phased-array antennas of superfast information processing systems and in multipurpose measuring devices. One of the main parameters of multi discrete

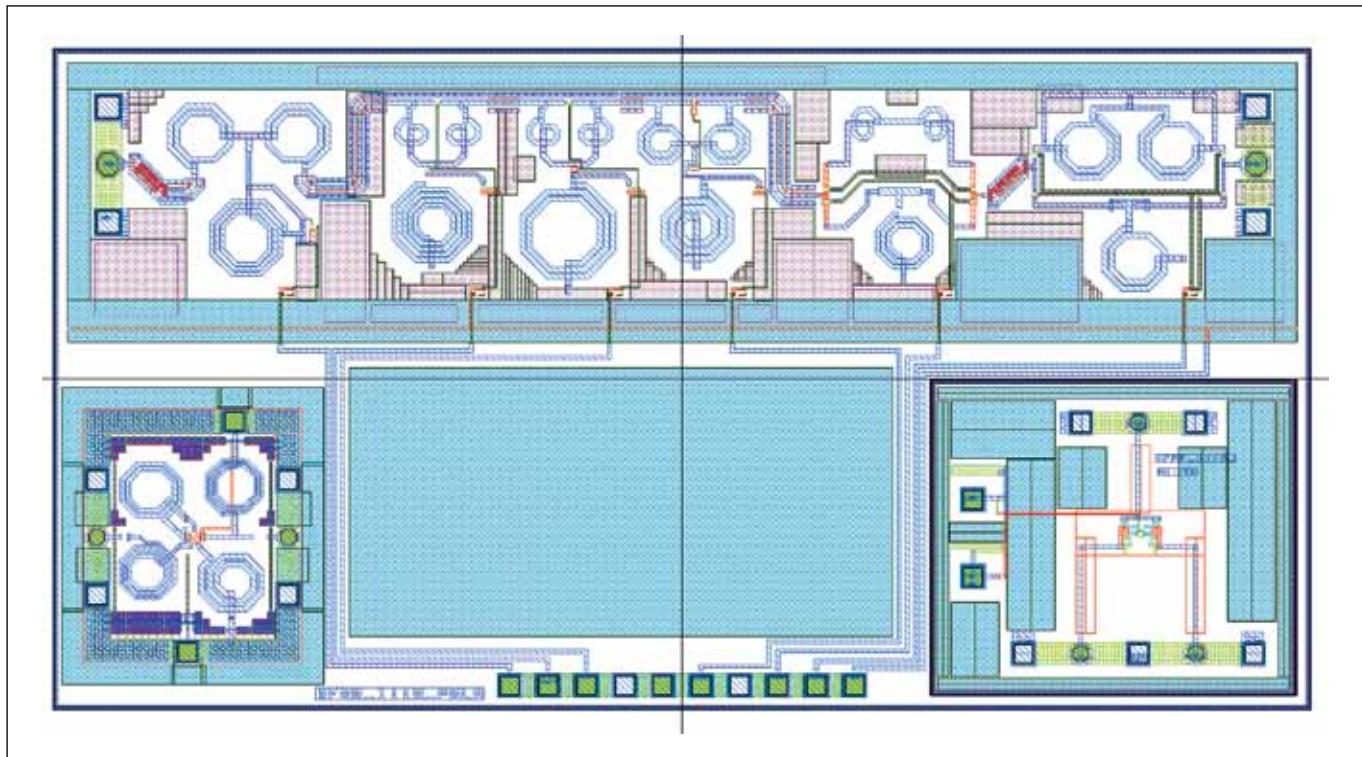

phase changer are the maximum phase shift and minimum discrete. Circuit diagram of the developed phase changer is shown in Fig.10. Fig.11 shows a test chip containing the phase changer, low noise amplifier and signal switch, which is connected to the bonding areas for measurements using an automated complex.

## CONCLUSION

A library of microwave components and CFBs for correct simulation of the electrical properties of microwave transistors at frequencies up to 12 GHz is developed. A set of CFBs obtained using these models

is presented. The characteristics of CFBs correspond to the level of technology.

Developed library will allow to model effectively complex digital-to-analog very large scale IC for the serial production at MERI and Mikron JSC. ■

The project is supported by the Ministry of education and science of the Russian Federation in the framework of the Federal target program "Research and development on priority directions of scientific and technological complex of Russia for 2014-2020" according to the agreement No.14.579.21.0072 dated 24 November 2014 (unique identifier of applied research RFMEFI57914X0072, code of project 2014-14-579-0129).

Таблица 4. Расчетные технические характеристики аттенюатора в сравнении с аналогами

Table 4. Design parameters of attenuator in comparison with analogues

| Параметр<br>Parameter                                                      | НИИМЭ и Микрон<br>MERI and Mikron     | [13]                          | [14]                                        | [15]                          |

|----------------------------------------------------------------------------|---------------------------------------|-------------------------------|---------------------------------------------|-------------------------------|

| Технология<br>Technology                                                   | КМОП КНИ 0,18 мкм<br>0.18 μm CMOS SOI | КМОП 0,18 мкм<br>0.18 μm CMOS | SiGe БиКМОП 0,25 мкм<br>0.25 μm SiGe BiCMOS | КМОП 0,18 мкм<br>0.18 μm CMOS |

| Диапазон частот, ГГц<br>Frequency range, GHz                               | 8–12                                  | 8,5–10                        | 8–11                                        | 8–12                          |

| Количество состояний<br>Number of states                                   | 128                                   | 128                           | 64                                          | 128                           |

| Коэф. передачи, дБ<br>Transmission gain, dB                                | -8                                    | -                             | -                                           | -10,5                         |

| СКО амплитудной<br>ошибки, дБ<br>Standard deviation of amplitude error, dB | 1,5                                   | 0,25                          | 1,5                                         | 0,4                           |

| Ток потребления<br>Current consumption                                     | 0                                     | 0                             | -                                           | -                             |

| Размер кристалла, мм <sup>2</sup><br>Chip size, mm <sup>2</sup>            | 0,2×0,15 (без КП)                     | 0,4×0,6 (без КП)              | 8,4 (приемо-передатчик)                     | 1,25×0,4                      |

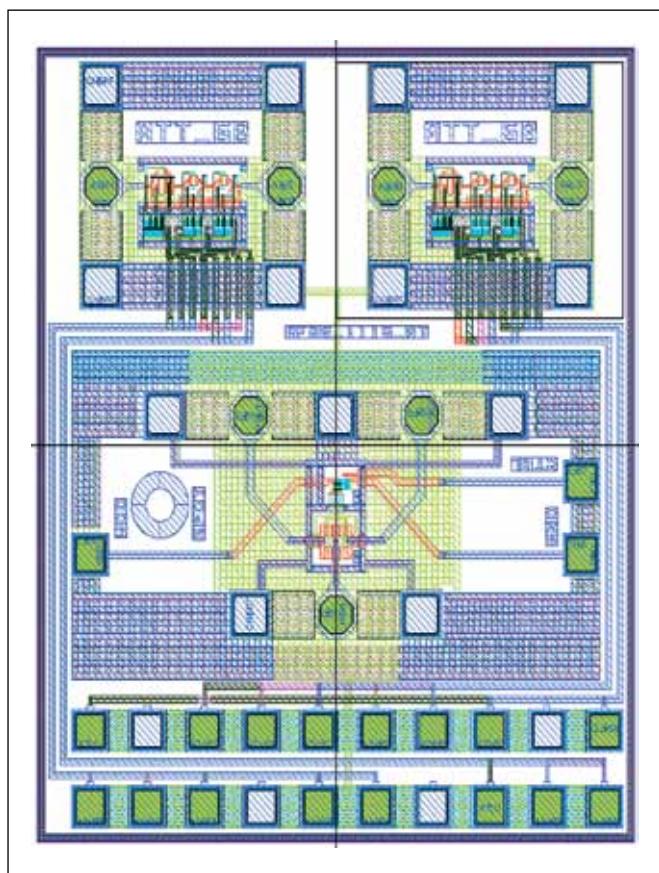

Рис.9. Топология тестового кристалла

Fig.9. Topology of the test chip

а на рис.9 – топология кристалла для экспериментальных исследований двух конструкций аттенюатора, различающихся интерфейсом управления и SPDT-переключателя, оптимизированного на частотный диапазон 8–12 ГГц.

Фазовращатели СВЧ наиболее употребительны в фазированных антенных решетках систем сверхбыстрой обработки информации, измерительной аппаратуре широкого назначения. Одним из основных параметров, характеризующих многодискретный фазовращатель, являются максимальный фазовый сдвиг и минимальный дискрет. Электрическая схема разработанного фазовращателя приведена на рис.10. На рис.11 показан тестовый кристалл, содержащий фазовращатель, малошумящий усилитель и переключатель сигналов, разведенный в контактные площадки для измерений с помощью автоматизированного комплекса.

## ЗАКЛЮЧЕНИЕ

Разработана библиотека СВЧ-элементов и СФБ, позволяющая корректно моделировать электрические характеристики СВЧ-транзисторов на частотах до 12 ГГц. Показан набор СФБ, полученных с использованием указанных моделей. Характеристики СФБ соответствуют уровню используемой технологии.

Рис.10. Электрическая схема цифрового фазовращателя

Fig.10. Circuit diagram for digital phase changer

Рис.11. Топология тестового кристалла

Fig.11. Topology of the test chip

Таблица 5. Расчетные технические характеристики фазовращателя в сравнении с аналогами

Table 5. Design parameters of phase changer in comparison with analogues

| Параметр<br>Parameter                                                      | НИИМЭ и Микрон<br>MERI and Mikron     | [13]                          | [16]                                                            | [17]                                                         |

|----------------------------------------------------------------------------|---------------------------------------|-------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|

| Технология<br>Technology                                                   | КМОП КНИ 0,18 мкм<br>0.18 μm CMOS SOI | КМОП 0,18 мкм<br>0.18 μm CMOS | SiGe БиКМОП,<br>0,42/0,25<br>мкм<br>0.42/0.25 μm SiGe<br>BiCMOS | SiGe БиКМОП,<br>0,18/0,13 мкм<br>0.18/0.13 μm SiGe<br>BiCMOS |

| Диапазон частот, ГГц<br>Frequency range, GHz                               | 9,5–10,5                              | 8,5–10                        | 8–12                                                            | 8,5–10,5                                                     |

| Количество состояний<br>Number of states                                   | 128                                   | 128                           | 64                                                              | 32                                                           |

| Коэф. передачи, дБ<br>Transmission gain, dB                                | -10                                   | -                             | -10,1                                                           | -17                                                          |

| СКО фазовой ошибки, град.<br>Standard deviation of phase<br>error, degree  | 5                                     | 2                             | 5                                                               | 3                                                            |

| СКО амплитудной<br>ошибки, дБ<br>Standard deviation of amplitude error, dB | 2,4                                   | -                             | 0,6                                                             | -                                                            |

| Ток потребления<br>Current consumption                                     | 0                                     | 0                             | 106@5В                                                          | 4,8@2,5В                                                     |

| Размер кристалла, мм <sup>2</sup><br>Chip size, mm <sup>2</sup>            | 2,9×0,5 (без КП)                      | 2,0×1,5<br>(без КП)           | 1,4×2,8                                                         | 1,1×1,9                                                      |

Разработанная библиотека позволит эффективно моделировать сложные цифро-аналоговые СБИС для дальнейшего изготовления по российскому серийному технологическому процессу фирмы ОАО "НИИМЭ и Микрон".

Работа выполнена при поддержке Министерства образования и науки Российской Федерации в рамках федеральной целевой программы "Исследования и разработки по приоритетным направлениям развития научно-технического комплекса России на 2014–2020 годы" по соглашению № 14.579.21.0072 от 24 ноября 2014 года (уникальный идентификатор прикладных научных исследований RFMEFI57914X0072, шифр работы 2014-14-579-0129).

## ЛИТЕРАТУРА

1. Красников Г.Я. Конструктивно-технологические особенности субмикронных МОП транзисторов. – М.: Техносфера, 2011. 800 с.

2. Jun L. Compact Modelling in RF CMOS Technology, 2011. 132 p.

3. Sze S.M. High speed semiconductor devices. New York, Wiley, 1990.

4. Van deer Ziel A. Noise in Solid State Devices and Circuits. John Wiley, 1986.

5. Liou J.J. and Schwierz F. RF-MOSFET: recent advances, current status and future trends. Solid-State Electronics. 2003. Vol. 47. No. 11. PP. 1881–1895.

6. Kinayman N., Bonilla M., Relcourse M., Redus J. High-Accuracy Digital 5-Bit 0.8–2 GHz MMIC RF Attenuator for Cellular Phones. Microwave Symposium Digest. 2001. Vol. 3. PP. 2231–2234.

7. <http://multicore.ru/index.php?id=1333>

8. [http://ntlab.com/IP/rus/Hard/Analog\\_Mixed/LNA/130iHP\\_LNA\\_04R.pdf](http://ntlab.com/IP/rus/Hard/Analog_Mixed/LNA/130iHP_LNA_04R.pdf)

9. Козловский Э.Ю., Осипов А.М., Селезнев Б.И. Особенности технологии СВЧ монолитной интегральной схемы малошумящего усилителя на основе GaAs рHEMT // Вестник Новгородского государственного университета. 2013. № 75 Т. 1.

10. Udayashankar S., Davidson M., Dhas K. Design and Performance Measure of 5.4 GHZ CMOS Low Noise Amplifier Using Current Reuse Technique in 0.18 μm Technology. International Journal of Hybrid Information Technology. 2014. Vol. 7. No. 1 (2014). PP. 157–166.

11. Salimath A. Harmonic performance evaluation of CMOS SOI SPDT switch with embedded lateral substrate model. International Symposium on Electronic System Design, pp. 187–190, 2010.

12. Tinella C., Fournier J.M., Belot D., Knopik V. A high-performance CMOS-SOI antenna switch

- for the 2.5–5-GHz band IEEE Journal of Solid-State Circuits. Vol. 38, Issue 7, July 2003.

13. Gharibdoust K., Mousavi N., Kalantari M., Moezzi M. A Fully Integrated 0.18 μm CMOS Transceiver Chip for -Band Phased-Array. IEEE Transactions on Microwave Theory and Techniques. Vol. 60. PP. 2192–2202, July 2012.

14. Jeong J. and Yom I. X-band high power SiGe BiCMOS multi-function chip for active phased array radars. Electron. Lett. Vol. 47. No. 10. PP. 618–619, Dec. 2011.

15. Bon-Hyun Ku, 6-bit CMOS Digital Attenuators With Low Phase Variations for X -Band Phased-Array Systems, IEEE Transactions on Microwave Theory and Techniques. Vol. 58. Issue 7. PP. 1651–1663, July 2010.

16. Елесин В.В., Назарова Г.Н., Усачев Н.А., Чуков Г.В., Сотсков Д.И. Построение монолитных ИС многоразрядных фазовращателей СВЧ-диапазона с улучшенными точностными характеристиками // Известия вузов. Электроника. 2012. № 5(97). С. 31–38.

17. Morton M.A., Comeau J.P., Cressler J.D. et al. Sources of phase error and design considerations for silicon-based monolithic high-low pass microwave phase shifters. – IEEE TMTT. 2006. Vol. 54. № 12. – P. 4032–4040.

## ФОРУМ SEMICON RUSSIA 2016

С 7 по 9 июня в Москве состоялся форум по микро- и наноэлектронике SEMICON Russia. В 2016 году организаторы сделали акцент на мероприятиях, имеющих своей целью представление полной картины цепочки поставок. В Форуме приняли участие российские и иностранные аналитики, поставщики и производители технологий, услуг и оборудования.

Первым мероприятием был "Российский стратегический симпозиум по высоким технологиям", который открыл деловую программу 7 июня. Симпозиум стал ключевым событием форума и привлек более 130 делегатов – представителей власти, российских и зарубежных менеджеров и инженеров.

Продолжили деловую программу следующие конференции: "Умные города", "Индустрия 4.0", "МЭМС для Интернета вещей", "Силовая электроника", "Гибкая электроника", "Мейкеры – рынок, формирующий рынки будущего". Спикерами выступили представители таких организаций, как Rosnano, imec, FlexEnable, Frost & Sullivan, MIRDC, "Ангстрем", Picosun, Fairchild Semiconductor, "Силовая электроника", PBK, Intel, SAP, Autodesk, Silicon Saxony, Fraunhofer. Также состоялся Российско-тайваньский технологический форум полупроводникового оборудования и перспектив отраслевого взаимодействия.

Выставка SEMICON Russia собрала на своей площадке 80 экспонентов, которые продемонстрировали передовые технологии, оборудование и пилотные проекты в сфере микроэлектроники и смежных направлений. В выставке приняли участие компании полупроводниковой отрасли из 15 стран мира, включая Россию, Австрию, Белоруссию, Бельгию, Китай, Чехию, Финляндию, Францию, Германию, Италию, Голландию, Южную Корею, Тайвань, Великобританию, США. Форум посетило более 1800 человек.

SEMI Russia & CIS