# РЕАЛИЗАЦИЯ ИНТЕРФЕЙСА SPACEWIRE В МИКРОПРОЦЕССОРАХ НИИСИ РАН ДЛЯ КОСМИЧЕСКОГО ПРИМЕНЕНИЯ

## IMPLEMENTING SPACEWIRE INTERFACE IN MICROPROCESSORS MANUFACTURED BY SRISA RAS FOR SPACE APPLICATIONS

УДК 621.382.2/.3, ББК 32.844.1, ГСНТИ 47.14.07, СПИН 1213-6377

НОВОЖИЛОВ Е. А.

*novozhil@niisi.msk.ru*

NOVOZHILOV E. A.

*novozhil@niisi.msk.ru*

ФГУ ФНЦ НИИСИ РАН

117218, Москва, Нахимовский просп., 36, к. 1

SRISA RAS

bld. 1, 36 Nakhimovskiy Ave., Moscow, 117218

Представлена унифицированная реализация интерфейса SpaceWire в разработанном НИИСИ РАН семействе микросхем для космического применения.

**Ключевые слова:** SpaceWire; микропроцессор.

The paper presents unified SpaceWire interface implementation in a series of microcircuits for space application developed by SRISA RAS.

**Keywords:** SpaceWire; micropocessor.

В НИИСИ РАН разработано семейство микросхем для космического применения. Это семейство включает в себя управляющий процессор, резервированный сбоестойчивый процессор, процессор поддержки ранее разработанных модулей с интерфейсом PCI, коммутатор интерфейсов SpaceWire. Эти микросхемы имеют унифицированную реализацию подсистемы SpaceWire, позволяющую строить системы на основе этого интерфейса. Микросхемы изготавливаются по техпроцессу с нормами 250 нм на отечественных фабриках, используются пластины кремний на изоляторе. Микросхемы собираются в герметичные металлокерамические корпуса. Далее в статье изложены основные решения, использованные при реализации подсистемы SpaceWire.

Интерфейс SpaceWire был разработан по заказу Европейского космического агентства (ЕКА) для унификации связи между устройствами в космических аппаратах. ЕКА выпустило несколько стандартов для обеспечения совместимости устройств, использующих данный интерфейс.

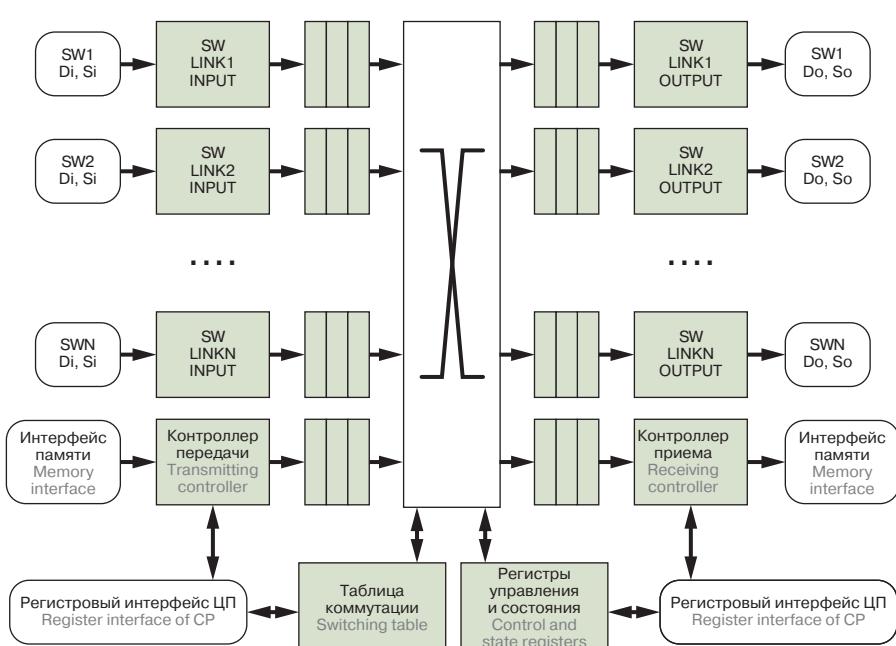

Унифицированная подсистема SpaceWire разработки НИИСИ РАН соответствует требованиям этих стандартов. Структурная схема подсистемы SpaceWire представлена на рис. 1.

Подсистема SpaceWire состоит из маршрутизатора, подключенных к нему внешних интерфейсных портов и системного интерфейсного порта, оснащенного контроллерами прямого доступа к памяти для приема и передачи пакетов.

Маршрутизатор состоит из неблокирующего коммутатора и таблицы коммутации. Он производит коммутацию и пересылку пакетов внутри сети SpaceWire, имеет несколько коммутируемых портов, одним из которых является системный интерфейсный порт. Внешние

порты совместимы со стандартом ЕКА ECSS-E-ST-50-12C. Для настройки, управления и диагностики подсистемы SpaceWire со стороны центрального процессора используются регистры управления и состояния.

### Характеристики основных устройств подсистемы SpaceWire.

Интерфейсный порт:

- интерфейсный порт соответствует стандарту ЕКА ECSS-E-ST-50-12C;

- порт использует дифференциальные сигналы (LVDS), электрические характеристики которых соответствуют стандарту ANSI/TIA/EIA-644;

- кодирование сигналов порта проводится в соответствии со стандартом IEEE 1355-1995.

Рис. 1. Структурная схема подсистемы SpaceWire

Fig. 1. Block diagram of SpaceWire subsystem

Контроллер прямого доступа к памяти:

- состоит из канала приема и канала передачи. Каналы функционируют независимо друг от друга;

- обеспечивает передачу данных из адресного пространства вычислительной системы в сеть SpaceWire и в обратном направлении без участия центрального процессора;

- программная модель построена с возможностью использования команд протокола RMAP в соответствии со стандартом EKA ECSS-E-ST-50-52C. Поддерживает идентификацию протокола в соответствии со стандартом EKA ECSS-E-ST-50-51C. Максимальная длина отправляемых и принимаемых пакетов данных составляет 16 Мбайт.

Является ведущим устройством на шине вычислительной системы.

Коммутатор:

- не блокирующая структура позволяет соединять любой входной порт с любым свободным выходным портом независимо от работы остальных портов;

- поддерживается несколько портов, один из которых является системным интерфейсным портом;

- поддерживается логическая адресация, в этом случае используется таблица коммутации;

The SRISA RAS has developed a series of microcircuits for space application. This series includes a control processor, a redundant/back-up hardened processor, a processor supporting previously developed modules with PCI interface, SpaceWire interface switch unit. These microcircuits have a unified implementation of SpaceWire subsystem, making it possible to build systems basing on this interface. Microcircuits manufactured by 250nm geometry size technology at domestic factories utilize silicon on insulator wafers. Microcircuits are assembled in hermetic cerametallic packages. The paper highlights the main solutions for SpaceWire subsystem implementation.

SpaceWire interface was custom-made for the European Space Agency (ESA) to unify communication between different devices in space vehicles. The ESA issued a number of standards to provide compatibility between devices utilizing this interface.

The unified SpaceWire subsystem developed by the SRISA RAS meets the requirements of these standards. Fig. 1 presents a block diagram of SpaceWire subsystem.

SpaceWire subsystem consists of a routing device, external interface ports connected to it and system interface port equipped with direct memory access controllers for receiving and transmitting packets.

The routing device consists of a non-blocking switchboard and a switching table. It produces switching and packets forwarding inside SpaceWire network, has several switching ports, one of them being a system

- поддерживается групповая адаптивная маршрутизация (group adapting routing);

- поддерживается широковещательные (broadcast) и групповые (multicast) способы передачи пакетов.

Автор считает, что в данной работе новыми являются следующие положения и результаты: разработаны унифицированные аппаратные средства для построения подсистемы SpaceWire, используемые в микросхемах для космического применения.

## ЛИТЕРАТУРА

1. IEEE Computer Society, "IEEE Standard for Heterogeneous Interconnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)", IEEE Standard 1355-1995.

2. IEEE Computer Society, "IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI)", IEEE Standard 1596.3-1996.

3. ESA Requirements and Standards Division. "SpaceWire. Links, Nodes, Routers and Networks", ECSS-E-ST-50-12C.

4. ESA Requirements and Standards Division. "SpaceWire Protocol Identification", ECSS-E-ST-50-51C.

5. ESA Requirements and Standards Division. "SpaceWire. Remote Memory Access Protocol", ECSS-E-ST-50-52C.

interface port. External ports are compatible with EKA ECSS-E-ST-50-12C standard. Control and state registers are used for tuning, controlling and checking SpaceWire subsystem from the side of central processor.

### Characteristics of Main SpaceWire Subsystem Devices

Interface Port:

- The interface port corresponds to EKA ECSS-E-ST-50-12C standard.

- The port uses differential signals (LVDS), whose electrical characteristics correspond to ANSI/TIA/EIA-644 standard.

- Port signals encoding is carried out in accordance with IEEE 1355-1995 standard.

Direct Memory Access Controller:

- Consists of receiving and transmitting channels. The channels operate independently of each other.

- Provides data transmission from address space of computation system into SpaceWire network and backwards without central processor participation.

- Software model allowing an opportunity of utilizing RMAP protocol commands was built up in compliance with EKA ECSS-E-ST-50-52C standard. It supports protocol identification in accordance with EKA ECSS-E-ST-50-51C standard. Maximum length of transmitted and received data packets is 16Mb.

- Performs the role of master device on the bus of computing system.

Switchboard:

- Non-blocking structure permits connecting any input port with any free output port independently of other ports operation;

- Supports several ports, one of which being a system interface port;

- Supports logical addressing; in this case the switching table is used;

- Supports group adaptive routing;

- Supports broadcast and multicast means of packets transfer.

The author considers that in this research the following provisions and results are novel: unified hardware tools have been developed for building SpaceWire subsystem used in microcircuits for space application.

## REFERENCES

1. IEEE Computer Society, "IEEE Standard for Heterogeneous Interconnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)", IEEE Standard 1355-1995.

2. IEEE Computer Society, "IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI)", IEEE Standard 1596.3-1996.

3. ESA Requirements and Standards Division. "SpaceWire. Links, Nodes, Routers and Networks", ECSS-E-ST-50-12C.

4. ESA Requirements and Standards Division. "SpaceWire Protocol Identification", ECSS-E-ST-50-51C.

5. ESA Requirements and Standards Division. "SpaceWire. Remote Memory Access Protocol", ECSS-E-ST-50-52C.