УДК 621.382.2/3

DOI: 10.22184/NanoRus.2019.12.89.202.210

# ТЕСТОВЫЕ КРИСТАЛЛЫ ДЛЯ РАСЧЕТНО-ЭКСПЕРИМЕНТАЛЬНОЙ ОЦЕНКИ РАДИАЦИОННОЙ СТОЙКОСТИ НАНОМЕТРОВЫХ КМОП СБИС СнК

## TEST CHIPS FOR EXPERIMENT-BASED RADIATION HARDNESS CALCULATION OF NANOMETER SYSTEMS-ON-CHIP

ГЕРАСИМОВ ЮРИЙ МИХАЙЛОВИЧ

GERASIMOV YURIY M.

ГРИГОРЬЕВ НИКОЛАЙ ГЕННАДЬЕВИЧ

GRIGORYEV NIKOLAY G.

КОБЫЛЯЦКИЙ АНДРЕЙ ВАДИМОВИЧ

andreykob@elvees.com

KOBYLYATSKIY ANDREY V.

andreykob@elvees.com

ПЕТРИЧКОВИЧ ЯРОСЛАВ ЯРОСЛАВОВИЧ

PETRICHKOVICH YAROSLAV YA.

АО «Научно-производственный центр «Электронные вычислительно-информационные системы»

124498, г. Москва, г. Зеленоград, проезд № 4922, 4, стр. 2

R&D Center "ELVEES", JSC

bld. 2, 4 Lane 4922, Zelenograd, Moscow, 124498, Russia

Предложена концепция создания тестовых кристаллов (ТК), сформулированы основные требования к структурам и блокам на ТК. Предложен типовой состав ТК для исследования возможностей и характеристики технологии по радиационной стойкости. Показано, что результаты исследований ТК позволяют прогнозировать радиационную стойкость СБИС расчетно-экспериментальными методами.

**Ключевые слова:** КМОП-транзисторы; система на кристалле; радиационная стойкость; радиационные эффекты; радиационно-стойкое проектирование; СФ-блок; тестовый кристалл.

The paper highlights a concept of the test chip (TC) design as well as basic requirements for structures and blocks on the TC. The typical TC composition has been proposed for studying the technology capabilities in terms of radiation hardness and characterization thereof. It has been shown that the results of TC examination make it possible to predict the radiation hardness of systems-on-chip or SRAM chips by calculation and experimental methods.

**Keywords:** test chip; CMOS transistors; system-on-chip; radiation hardness; radiation effects; radiation-hardening-by-design; IP-block.

### ВВЕДЕНИЕ

Важным этапом радиационно-стойкого проектирования нанометровых КМОП СБИС типа «система на кристалле» (СнК) и ОЗУ (далее — СБИС) является разработка и исследование тестовых кристаллов (ТК), содержащих специальные физические структуры, элементы и блоки. В стандартном маршруте проектирования этап разработки и исследования ТК может занимать различное положение в зависимости от назначения ТК. Так, например, данный этап может предшествовать началу разработки перспективной СБИС, когда необходимо качественно оценить параметры разрабатываемого изделия, или являться промежуточным этапом в качестве макетного образца.

В настоящее время в АО НПЦ «ЭЛВИС» для базовых отечественных и зарубежных КМОП-технологий объемного кремния от 250 нм до 90 нм разработано, изготовлено и исследовано большое количество ТК. Результаты исследований ТК позволили создать высокопроизводительные и конкурентоспособные СБИС СнК с повышенной стойкостью к радиационным факторам космического пространства. В данной работе представлено описание блоков и структур для проведения радиационных исследований, на основании которых разработана методика расчетно-экспериментальной оценки дозовой стойкости СБИС.

### КОНЦЕПЦИЯ СОЗДАНИЯ ТЕСТОВЫХ КРИСТАЛЛОВ

Разработка тестовых кристаллов производится в целях проведения комплекса предварительных исследований и испытаний,

необходимых для достижения наилучших параметров качества перспективного проекта. Комплекс исследований включает в себя следующее.

1) Исследование особенностей проявления доминирующих радиационных эффектов в структурах и элементах СБИС по конкретной технологии. Высокий уровень стойкости может быть обеспечен технологическим переходом между проектными нормами без применения специальных методов [1]. Таким способом, например, повышается дозовая стойкость и стойкость к тиристорному эффекту (ТЭ), что объясняется масштабированием технологических параметров МОП-структур, таких как концентрация примесей в подложке и кармане, глубина залегания n+/p+-областей, карманов и изоляции, толщина подзатворного окисла и др. Исследования особенностей проявления ТЭ на разработанных ТК показали, что в логической части СнК, разработанной по технологии 90 нм без применения специальных методов, ТЭ в достаточно широком диапазоне линейных потерь энергии ( $LPE > 60 \text{ МэВ} \cdot \text{см}^2/\text{мг}$ ) частицы не проявляется. Таким образом, в технологии 90 нм для обеспечения достаточно высокой стойкости логических элементов к ТЭ при воздействии тяжелых частиц не требуются сплошные p+ охранные кольца, применяемые на более высоких проектных нормах.

Следует отметить, что на одном уровне проектной нормы на различных фабриках или опциях одной технологии могут быть получены отличающиеся параметры РС. Это обусловлено различием технологий между собой на одном уровне проектных норм

Таблица 1. Параметры транзисторов и структур, определяющих радиационную стойкость СБИС

Table 1. Parameters of transistors and structures determining radiation hardness of VLSIs

| Параметр<br>Parameter                                                                                                                   | Значение параметра для проектных норм<br>The parameter value for different technology nodes |          |                |                    |                |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------|----------------|--------------------|----------------|

|                                                                                                                                         | 180                                                                                         | 130      | 90             | 90                 | 65             |

| Фабрика   Foundry                                                                                                                       | «Микрон»<br>Mikron                                                                          | Silterra | TSMC           | «Микрон»<br>Mikron | TSMC           |

| Напряжение питания ядра, В<br>Core power voltage, V                                                                                     | 1,8                                                                                         | 1,2      | 1,2            | 1,2                | 1,2            |

| Толщина подзатворного окисла, нм<br>Gate oxide thickness, nm                                                                            | 3,2                                                                                         | 2,0      | 2,8-n<br>3,0-p | 2,1                | 2,6-n<br>2,8-p |

| Минимальная ширина канала транзистора, нм<br>Minimum transistor channel width, nm                                                       | 280                                                                                         | 150      | 120            | 120                | 120            |

| Минимальная длина канала транзистора, мкм<br>Minimum transistor channel length, $\mu$ m                                                 | 180                                                                                         | 130      | 100            | 60                 | 60             |

| Минимальное расстояние между n+-областями, мкм<br>Minimum spacing between n+ regions, $\mu$ m                                           | 0,32                                                                                        | 0,21     | 0,14           | 0,11               | 0,11           |

| Минимальное расстояние между n+-областью и n-карманом, нм<br>Minimum spacing between n+ region and n-well, nm                           | 0,40                                                                                        | 0,31     | 0,22           | 0,16               | 0,16           |

| Пороговое напряжение HVT тр-па, В<br>HVT transistor threshold voltage, V                                                                | n                                                                                           | 0,59     | 0,44           | 0,42               | 0,46           |

|                                                                                                                                         | p                                                                                           | 0,54     | 0,46           | 0,44               | 0,51           |

| Удельный прямой ток HVT тр-па, мкА/мкм<br>Saturation current of an HVT transistor, $\mu$ A/ $\mu$ m                                     | n                                                                                           | 497      | 358            | 378                | 368            |

|                                                                                                                                         | p                                                                                           | 202      | 155            | 166                | 173            |

| Удельный ток утечки HVT тр-па по стоку<br>(T = 25 °C), пА/мкм<br>Drain leakage current of an HVT transistor<br>(T = 25 °C), pA/ $\mu$ m | n                                                                                           | 5        | 17             | 12                 | 9              |

|                                                                                                                                         | p                                                                                           | 7        | 11             | 11                 | 14             |

| Асимптотическая задержка (M = 1, HVT), пс<br>Asymptotic delay (M = 1, HVT), ps                                                          | 29,3                                                                                        | 23,1     | 17,7           | 20,7               | 13,9           |

| Площадь однопортовой ячейки памяти, мкм <sup>2</sup><br>The area of a single-port memory cell, $\mu$ m <sup>2</sup>                     | COTS*                                                                                       | 4,98     | 2,43           | 1,15               | 0,525          |

|                                                                                                                                         | RHBD**                                                                                      | 9,18     | 5,49           | 3                  | 1,21/1,36      |

| Критический заряд, фКл<br>Critical charge, fC                                                                                           | COTS                                                                                        | 6,3      | 2,5            | 1,1                | 0,8            |

|                                                                                                                                         | RHBD                                                                                        | 18,3     | 12             | 6                  | —              |

\* COTS — Commercial off-the-shelf, \*\* RHBD — Radiation-Hardened-by-Design

## INTRODUCTION

Design and examination of test chips (TC) containing specific physical structures, elements and blocks are an important stage of radiation hardening-by-design of nanometer CMOS VLSIs of “system-on-chip” and SRAM types (further on referred to as VLSIs). The stage of test chip design and examination may take a different position in the standard design flow depending on the test chip purpose. For instance, this stage may precede the development of a promising VLSI when it is necessary to evaluate the parameters of the device being developed, or it may be an intermediate stage if it is necessary to make a prototype.

ELVEES R&D Center, JSC, by far has developed, manufactured and examined a large number of test chips produced

according to basic Russian bulk CMOS 250 nm to 90 nm technologies and those of other countries. The results of test chip examination allowed creating high-performance and competitive VLSI SoCs with higher space radiation hardness. This paper describes some blocks and structures to be used for radiation hardness examination which served as a basis for the method of experiment-based calculation of VLSI dose hardness.

## THE CONCEPT OF TEST CRYSTAL DESIGN

Test chips are developed for a set of preliminary studies and tests required to provide the best quality characteristics of the future design. The set of studies includes the following steps:

1. The study of particular manifestations of the dominant radiation effects in VLSI structures and elements produced according to the given technology. A high level of radiation hardness can be achieved by technologic transition to new design rules without using any special methods [1]. In such a way dose hardness and latch-up tolerance can be achieved by scaling such technology parameters of MOS structures as dopant concentration in the substrate and the well, depth of n+/p+ areas, wells and insulation, thickness of the gate oxide, etc. The study of the particular latch-up manifestations in the test chips developed according to 90 nm process without using any specific methods has shown that latch-up does not occur in a rather wide range of linear energy transfer of the particle (>60 MeV·cm<sup>2</sup>/mg). Thus 90 nm process does

в уровнях легирования, толщинах окислов, глубинах залегания областей и др., а также в качестве изготовления, например, в температурных режимах выращивания окислов [2], технологических разбросах [3] и т. д. В табл. 1 представлены основные параметры транзисторов и структур, определяющие радиационную стойкость СБИС. Видно, что большая часть параметров масштабируется по определенному правилу за исключением напряжения питания, толщины подзатворного окисла, порогового напряжения и тока утечки транзисторов. Это обусловлено проявлением короткоканальных эффектов и необходимостью коррекции технологического маршрута изготовления приборов. Различия в расчетных значениях тока утечки транзисторов на разных фабриках одного уровня проектных норм 90 нм достигают 30 %.

2) *Сравнение эффективности различных технических решений повышения радиационной стойкости СБИС, выработка рекомендаций по их использованию.* В связи переходом на новые проектные нормы пересматриваются подходы и методы проектирования, которые должны быть адаптированы под новые правила проектирования и проверены на эффективность. Например, при переходе с уровня 250 нм на 65 нм частота одиночных сбоев в статических ОЗУ уменьшается в 60 раз [4] за счет уменьшения площади ячейки памяти. Вклад уменьшения порогового значения ЛПЭ в частоту одиночных сбоев при этом оказывается несущественен. Поэтому использование транзисторов с повышенной шириной канала в ячейке памяти для уменьшения частоты одиночных сбоев становится неэффективным. При этом акцент в проектировании смещается в сторону многократных сбоев в нескольких разрядах одного слова, неисправляемых стандартными средствами помехоустойчивого кодирования. Следует проанализировать методы проектирования, направленные на снижение скорости накопления одиночных ошибок в накопителе, одним из которых, в частности, является использование транзисторов с повышенной шириной канала, и подавление многократных сбоев в одном информационном слове.

3) *Аттестация элементов и СФ-блоков на соответствие требуемым техническим параметрам для проектирования СБИС, отработки алгоритмов тестирования и взаимодействия между составными частями и блоками перспективной СнК.* В данном

не требуют полных  $p+$  гвардейских колец для обеспечения достаточной выносливости логических элементов, подвергнутых воздействию массивных частиц, в отличие от тех, что используются на более высоких технологических узлах.

It should be noted that different foundries or technology options may yield different radiation hardness performance even at the same technology node. This is due to the differences in particular technologies at the same technology node in terms of impurity level, oxide thickness, region depths, and so on as well as the differences in manufacturing quality, for example, temperature conditions of oxide growth [2], manufacturing tolerance [3], etc. Table 1 lists the key parameters of transistors and structures determining VLSI radiation hardness. It can be seen that most of the parameters are scaled according to a particular rule, except for power voltage, gate oxide

thickness, threshold voltage and transistor leakage current. The reason for this is short-channel effects and the necessity of technology adjustment of the device manufacturing process. The difference in the leakage current of 90 nm transistors produced at different foundries may be as high as 30 %.

2. The comparison of the effectiveness of various technology solutions meant to improve VLSI radiation hardness, and the development of recommendations for the application thereof. The transition to the new design rules requires the approaches and design methods to be reconsidered, adapted to the new rules and proved in terms of efficiency. For example, as a result of the transition from 250 nm to 65 nm, the single error rate in the static SRAMs reduces by a factor of 60 [4] due to the memory cell area reduction. In this case the contribution of the

случае ТК является полноценным прототипом, результаты исследования которого являются максимально приближенными к опытному варианту СнК.

СФ-блоки и библиотеки цифровых элементов разрабатываются в рамках единой методологии проектирования, в том числе и с ориентацией на РС, и формируют среду проектирования для разработчиков СнК [5]. Параметры стойкости используемых при проектировании СнК СФ-блоков и библиотек элементов определяют стойкость самой СнК. Поэтому они должны быть предварительно аттестованы на соответствие требованиям по критериям РС.

Таким образом, ТК охватывает достаточно широкий круг направлений исследований, проведение которых является экономически оправданным при разработке серии микросхем для массового производства в рамках одного техпроцесса. В связи с этим к тестовым структурам, элементам и блокам на ТК, предъявляются следующие требования.

1. Реализуемость — принципиальные возможности по осуществлению эксперимента; при разработке тестов должны быть учтены возможности оборудования, тестовой обвязки, влияния внутренних схем и внешних факторов на методику проведения эксперимента и получение конечных результатов.

2. Информативность результатов — извлечение максимального количества информации из проведенных исследований.

3. Наглядность результатов — показательность и потенциальные возможности сравнительного анализа должны обеспечивать результатам пригодность для дальнейшего использования.

4. Универсальность — проведение максимально возможного количества экспериментов на одном тестовом элементе.

5. Время- и ресурсозатратность — количество материальных, человеческих, временных и других ресурсов, необходимых для проведения эксперимента.

Зачастую для проведения полного комплекса испытаний одного ТК оказывается недостаточно, что может быть обусловлено, например, ограничениями по площади кристалла или количеством внешних выводов. Экономически оправданым оказывается выпуск нескольких ТК на одной пластине

reduction in the threshold value of the linear energy transfer to the single error rate is insignificant. That is the reason why it becomes inefficient to use transistors with wider channels in a memory cell in order to reduce the single error rate. Thus the focus of the design process shifts to multiple upsets in several bits of one word which cannot be rectified by the standard means of anti-noise coding. The design methods aimed at reducing the single error accumulation rate in the storage circuit should be considered, some of which use transistors with a wider channel and suppressing multiple upsets in one data word.

3. Certification of elements and IP-blocks as compliant with the data sheets on VLSI design and algorithms of testing and interoperability of the components and blocks of the prospective SoCs. In this context the test chip

по принципу MPW (Multi-Project Wafer), при этом появляется возможность проводить исследования параллельно и получать результаты гораздо быстрее.

### ТИПОВОЙ СОСТАВ ТЕСТОВЫХ КРИСТАЛЛОВ

Заданные требования позволяют сформировать типовой состав ТК, необходимый и достаточный для проведения полного комплекса испытаний, позволяющих получить максимально информативные и наглядные результаты. Состав включает элементы и блоки для статических и динамических исследований, что позволяет выявить наихудшие условия функционирования блоков и наиболее критичные узлы и цепи.

В соответствии с доминирующими радиационными эффектами [6], проявляющимися в нанометровых СБИС, набор структур и элементов на тестовых кристаллах содержит следующие изолированные домены и блоки.

1. Большие массивы физических структур, различных типов МОП-транзисторов, библиотечных элементов и ячеек памяти для определения их параметров при стационарном облучении в различных электрических режимах для характеристики элементов библиотек по РС.

2. Набор кольцевых генераторов, состоящих из элементов различных библиотек для исследования влияния ионизирующего облучения на их быстродействие и ток утечки.

3. Матрицы ячеек памяти и блоки памяти с различными схемотехническими и конструктивно-топологическими решениями для исследования эффекта «зашелкивания» при воздействии тяжелых частиц (ТЧ), оценки параметров сбоестойчивости в целях выбора оптимальных решений для РС СФ-блоков памяти различных типов.

4. Специальные тесты для исследования сбоестойчивости (и ионизационной реакции) различных элементов и структур при воздействии тяжелых частиц (ТЧ).

5. Стандартные и специализированные интерфейсные (LVDS, SpaceFibre, SSTL и др.) площадочные элементы для их исследования на стойкость к статическому электричеству.

6. Аттестуемые СФ-блоки.

В общем случае тестовые структуры и блоки для радиационных исследований можно классифицировать в зависимости от радиационного воздействия и исследуемого эффекта (табл. 2). Как видно из таблицы, наиболее полными, универсальными и информативными тестовыми блоками являются логические элементы, кольцевые генераторы и СФ-блоки памяти. Данные блоки позволяют провести полный комплекс испытаний как в статическом, так и в динамическом режиме в приближенных к реальному функционированию условиях.

Набор элементов, разработанных в соответствии с рассмотренными выше требованиями к тестовым структурам, позволяет определить предельные и компромиссные возможности технологического процесса по радиационной стойкости и в дальнейшем проводить оценки стойкости СБИС к дозовым радиационным эффектам расчетно-экспериментальными методами. Предложенный состав ТК позволяет оценить влияние технологических разбросов, мощности дозы или флюенса частиц, температуры и напряжений питания на параметры радиационной стойкости, быстродействия, потребляемой мощности исследуемых и разрабатываемых элементов и блоков.

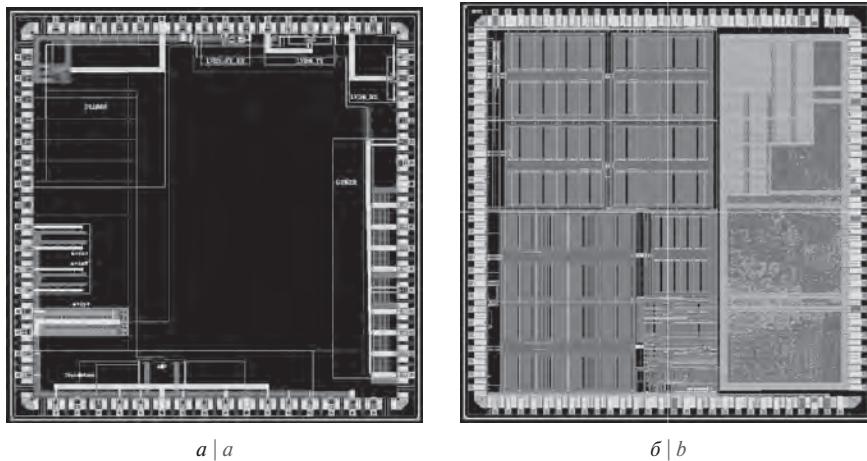

В идеальном случае на разных этапах проектирования достаточно исследовать два ТК: первый — «экспериментальный ТК» с тестовыми структурами и блоками, второй — «аттестационный ТК» с готовыми СФ-блоками, разработанными по результатам исследований первого ТК. На рис. 1 представлен подобный подход, реализованный по технологии 90 нм.

Ниже подробно рассматриваются особенности разработки структур и блоков для экспериментального ТК.

### СТРУКТУРЫ И БЛОКИ ДЛЯ РАСЧЕТНО-ЭКСПЕРИМЕНТАЛЬНОЙ ОЦЕНКИ ДОЗОВОЙ СТОЙКОСТИ СБИС СнК

Прогнозирование стойкости СБИС к дозовым радиационным эффектам в условиях возрастающей степени интеграции и преобладающей роли паразитных структур является актуальной задачей, поскольку большинство существующих методов основаны на сложных математических вычислениях на уровне отдельных транзисторов и структур. Результаты таких вычислений зачастую

is a fully functional prototype, whose examination results are closest to those of the experimental variant of the SoC.

IP-blocks and digital element libraries, including the radiation-hardened ones, are developed in the framework of the single design methodology and form the design environment for SoC designers [5]. The radiation hardness of the IP-blocks and element libraries used in the design determine the radiation hardness of the whole SoC. That is why they should be pre-certified as compliant with the radiation hardness requirements.

Consequently, the test chip addresses a rather wide range of research fields which are economically viable when designing a line of mass-produced ICs in one process flow. In this regard, the test structures, elements, and blocks on the test chip should comply with the following requirements:

1. Practicability — a possibility to carry out the experiment in principle, the capabilities of the equipment and test harness as well as the impact of internal circuits and external factors on the experimental method should be taken into consideration during the test design.

2. Informative value of the results — obtaining maximum information content from the performed research.

3. Illustrative value of the results — the representativeness and the potential for comparative analysis should make the results suitable for further usage.

4. Multipurposeness — performing as many experiments on one test element as possible.

5. Time and resource efficiency — the material, human, time and other resources required for the experiment.

It is not infrequently when one test chip is not sufficient for the full test cycle, which can be accounted for by the limited chip area or the number of external terminals. Manufacturing several test chips on one wafer using MPW (Multi-Project Wafer) principle proves to be economically viable. Another advantage of this approach is the possibility to perform research simultaneously and obtain the results much quicker.

### TYPICAL COMPOSITION OF TEST CRYSTALS

The above stated requirements determine the typical composition of a test chip necessary and sufficient for performing the whole set of tests and obtaining as informative and representative results as possible. The composition includes elements and blocks for static and dynamic tests, which makes it possible

Таблица 2. Структуры и блоки для радиационных исследований

Table 2. Structures and blocks for radiation examination

| Тестовая структура/блок<br>Test structure/block                                                             | Дозовые<br>эффекты<br>Dose effects | Одиночные и многократ-<br>ные эффекты (SEU, SET,<br>MCU, MBU)<br>Single or multiple effects<br>(SEU, SET, MCU, MBU) | Тиристорный<br>эффект (SEL)<br>Latch-up (SEL,<br>pulse IR) | УБР, ВПР<br>Dose rate effects | Статические (С)<br>или динамиче-<br>ские (Д) тесты<br>Static (S) or<br>dynamic (D) tests |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------|

| Физические структуры<br>(n+-n+, n+-n-карман, p-n-p-n)<br>Physical structures<br>(n+-n+, n+-n-well, p-n-p-n) | +                                  | —                                                                                                                   | +                                                          | —                             | C   S                                                                                    |

| Транзисторы<br>Transistors                                                                                  | +                                  | —                                                                                                                   | —                                                          | —                             | C   S                                                                                    |

| Логические элементы<br>Logical elements                                                                     | +                                  | ±                                                                                                                   | +                                                          | +                             | C+D   S+D                                                                                |

| Кольцевой генератор<br>Ring oscillator                                                                      | +                                  | +                                                                                                                   | +                                                          | +                             | C+D   S+D                                                                                |

| Массив ячеек памяти<br>Memory cell array                                                                    | +                                  | —                                                                                                                   | +                                                          | —                             | C   S                                                                                    |

| СФ-блоки памяти<br>IP memory blocks                                                                         | +                                  | +                                                                                                                   | +                                                          | +                             | C+D   S+D                                                                                |

не представляется возможным экстраполировать на конкретную СБИС, содержащую несколько миллиардов транзисторов и структур, из-за большого количества переменных, определяющих стойкость микросхемы, и неизбежного влияния разбросов технологических параметров КМОП-структур.

Проанализировать влияние различных факторов на дозовую стойкость отдельных КМОП-элементов позволяет приборно-технологическое моделирование с помощью SPICE-подобных симуляторов, встроенных в САПР, таких как, например, Synopsys TCAD. При этом для прогнозирования стойкости пользователю необходимо обладать точной, чаще всего конфиденциальной информацией о параметрах технологического процесса. Другим источником данных могут являться результаты экспериментов и исследований

тестовых структур и элементов. При использовании набора экспериментальных данных задача сводится к аппроксимации результатов экспериментов в САПР и обеспечению их наиболее близкого соответствия модели. Учитывая большое количество переменных, процесс аппроксимации и трехмерного моделирования с учетом различных краевых эффектов оказывается времязатратным, а результаты прогнозирования стойкости СБИС при этом могут сильно отличаться от реальной стойкости. Это связано с тем, что в стандартных коммерческих версиях САПР отсутствуют модели, адекватно описывающие зависимости электрофизических параметров от температуры и радиационных факторов [7]. Поэтому в общем случае такие САПР являются исследовательскими и предназначены для проведения качественного анализа процессов,

to identify the worst functioning conditions for blocks as well as the most critical nodes and circuits.

In accordance with the radiation effects [6] prevailing in nanometer VLSIs, the set of structures and elements on test chips contains the following isolated domains and blocks:

1. Large arrays of physical structures, MOS transistors of various types, library elements and memory cells to quantify their parameters upon exposure to steady state radiation in different electric modes to characterize the radiation hardness of the library elements.

2. A set of ring oscillators consisting of elements of different libraries to study the effect of ionizing radiation on their operating speed and leakage current.

3. Arrays of memory cells and memory blocks demonstrating various schematic, topological and constructive solutions to study the latch-up upon exposure

to massive particles and high-power pulse ionizing radiation and to evaluate the failure tolerance characteristics in order to select the optimal solution for radiation-hard IP-blocks of different memory types.

4. Special tests to examine failure tolerance (and ionization response) of various elements and structures upon exposure to massive particles.

5. Standard and custom interface (LVDS, SpaceFibre, SSTL and so on) area elements to study their static electricity tolerance.

6. The IP-blocks being certified.

In general the test structures and blocks to be used in radiation hardness examination can be classified according to the radiation exposure and the effect being studied (Table 2). As can be seen from the table, the most complete, multipurpose and informative test blocks are logic elements, ring oscillators and IP memory blocks. These blocks allow a whole set of tests both in the static and

the dynamic modes under the conditions close to real functioning.

The set of elements designed in accordance with the above requirements for test structures allows identifying the limit and tradeoff capabilities of the process in terms of radiation hardness as well as evaluating the VLSI tolerance to dose radiation effects using calculation and experimental methods. The proposed composition of the test chip makes it possible to evaluate the impact of manufacturing tolerance, dose rate, fluence of particles, temperature and power voltages on radiation hardness, operating speed and consumed power of the elements and blocks being examined and developed.

Ideally it would be sufficient to examine two test chips at different design stages: the first — ‘experimental’ test chip with test structures and blocks, the second — ‘certification’ test chip with ready IP-blocks developed on the basis of the first test chip examination.

Рис. 1. Топологии ТК по технологии 90 нм: а) экспериментальный, б) аттестационный

Fig. 1. 90 nm test chip topologies: a — experimental; b — certification

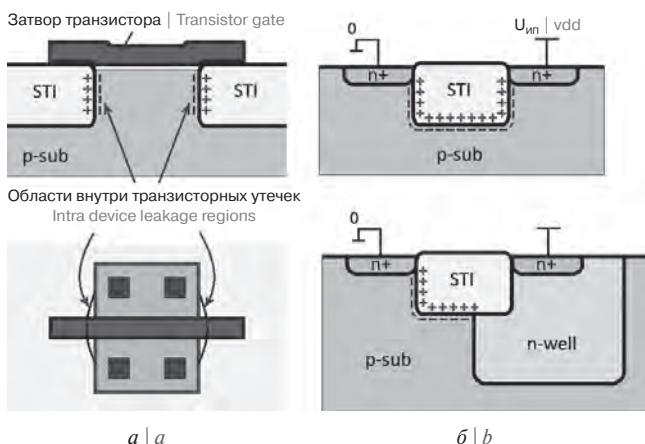

Рис. 2. Паразитные каналы утечки в КМОП-структуратах: а) внутритранзисторные, б) межприборные

Fig. 2. Parasitic leakage paths in CMOS structures: a) intratransistor; b) interdevice

Figure 1 demonstrates this approach implemented in 90 nm process.

The development of the structures and blocks of the experimental test chip is described below in detail.

### STRUCTURES AND BLOCKS FOR EVALUATING THE VLSI SOC RADIATION HARDNESS BY MEANS OF EXPERIMENT-BASED CALCULATION

Predicting VLSI tolerance to dose radiation effects in the context of growing integration and prevailing role of parasitic structures is a critical task because most of the existing methods are based on complex mathematical calculations at the level of separate transistors and structures. The results of such calculations cannot always be extrapolated to a specific VLSI containing several billion transistors and structures due to a large number of variables determining the chip tolerance

and the inevitable impact of manufacturing tolerance of the CMOS structure.

Instrumental and process simulation using SPICE simulators embedded in CAD systems such as, for example, Synopsys TCAD, allows analysing the impact of various factors on the dose hardness of separate CMOS elements. In the meanwhile, the user has to have accurate, and often confidential, information about the parameters of the process to predict the radiation hardness. The results of experiments and examination of test structures and elements can be another source of data. When using a set of experimental data, the task reduces itself to approximating the experimental results in a CAD system and providing their closest possible correspondence to the model. Taking into consideration the number of variables, the process of approximation and 3D simulation with due account of various edge effects proves to be time- and resource-consuming

происходящих при воздействии радиации на КМОП-элементы.

Разработан расчетно-экспериментальный метод прогнозирования дозовой стойкости СБИС, основанный на характеризации стандартных цифровых элементов и СФ-блоков ОЗУ по стойкости к стационарному ионизирующему излучению по результатам исследований тестовых структур и элементов на ТК.

Имеющиеся в настоящее время теоретические представления и экспериментальные данные показывают, что уровень дозовой стойкости современных микросхем определяется параметрическим отказом по статическому току потребления. Статический ток потребления является аддитивной величиной и складывается из токов утечки отдельных транзисторов и структур. При этом ток утечки транзисторов подразделяется на собственный ток утечки и радиационно-индуцированный ток утечки. Собственный ток утечки транзисторов складывается из подпорогового тока утечки и тока утечки p-n-переходов. В нанометровых транзисторах добавляются также составляющие тока утечки через затвор и ток утечки, индуцируемый потенциалом на стоке [8].

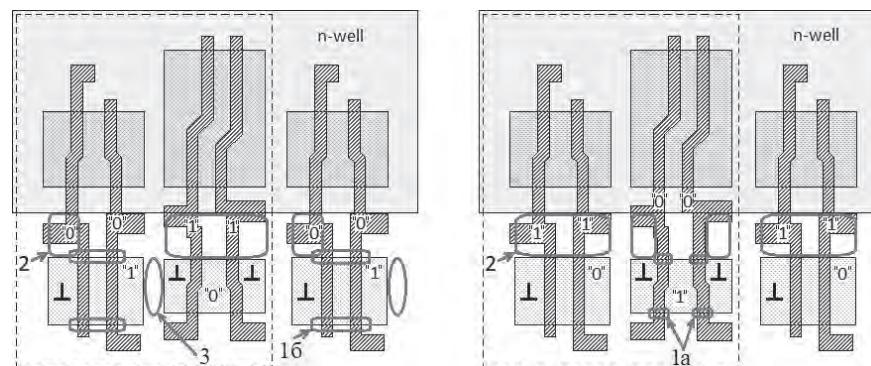

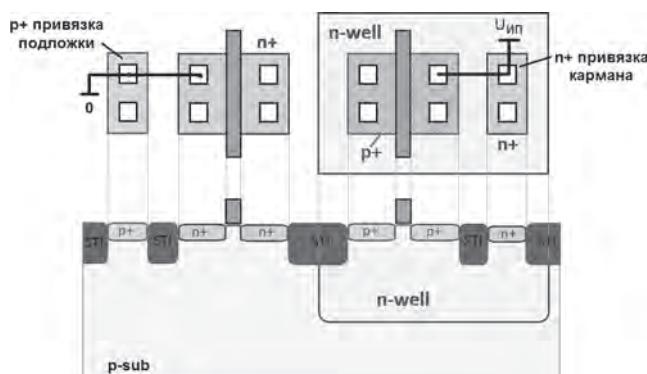

Радиационно-индуцированный ток утечки n-MOP-транзисторов обусловлен накоплением положительного заряда в STI-окисле, отпиранием паразитных n-MOP-транзисторов и возникновением паразитных каналов утечки, которые в общем случае делятся на межприборные и внутритранзисторные. На рис. 2 представлены КМОП-структуры каналов утечки в разрезе, а на рис. 3 и 4 данные утечки обозначены на уровне библиотечных элементов и ячеек памяти в зависимости от состояния входов элементов и статического состояния ячеек памяти.

Таким образом, по результатам дозовых исследований структур n+-n+ и n+-n-карман и транзисторов в различных режимах

and the predicted results of VLSI radiation hardness may be far from the actual ones. This is due to the fact that standard commercial versions of CAD systems lack models describing the dependencies of physical parameters on the temperature and radiation factors [7]. Therefore, generally speaking, these CAD systems are the research ones and are intended for a high-quality analysis of the processes taking place under the exposure of CMOS elements to radiation.

An experiment-based calculation method of predicting VLSI dose hardness has been developed, which is based on characterization of standard digital elements and SRAM IP-blocks in terms of tolerance to steady-state ionizing radiation using the results of examination of test structures and elements on the test chip.

The presently available theoretical models and experimental data show that the level of dose hardness of up-to-date chips

при облучении [9] создаются радиационные модели логических элементов в зависимости от состояний входов и ячеек памяти в зависимости от записанной информации в СФ-блок ОЗУ. Для различных значений уровня накопленной дозы формируются файлы характеристики, позволяющие еще на этапе статического временного анализа проекта оценить уровень ее дозовой стойкости.

В настоящее время метод проходит апробацию по технологии 90 нм. Проведение комплекса радиационных испытаний в полном объеме в различных температурных и режимных условиях на нескольких кристаллах позволит оценить точность такого подхода с учетом технологических разбросов параметров приборов.

### СТРУКТУРЫ И БЛОКИ ДЛЯ ИССЛЕДОВАНИЯ ОБЪЕМНЫХ РАДИАЦИОННЫХ ЭФФЕКТОВ В СБИС СнК

Объемные радиационные эффекты в СБИС возникают при попадании тяжелых частиц в активные структуры [6]. Наибольший интерес с точки зрения исследования на ТК представляют одиночные (SEU, SET) и многократные (MBU, MCU) эффекты в логических элементах и элементах памяти, а также тиристорный эффект (ТЭ, SEL).

Исследовать кратковременные импульсы напряжения (SET), возникающие при попадании ТЧ в цифровые элементы, позволяет массив последовательно соединенных логических элементов с соответствующим тестовым окружением, необходимым для измерения импульсов с очень малой длительностью

Рис. 3. Радиационные модели цифровых элементов с обозначением радиационно-индукционных токов утечки: 1a — утечка отдельного nMOPТ; 1b — утечка последовательно соединенных nMOPТ; 2) межприборные утечки n+-n-карман, 3 — межприборные утечки n+-n+, «0», «1» — логические состояния при облучении/измерении

Fig. 3. The radiation models of digital elements with the radiation-induced leakage currents indicated: 1 — interdevice n+-n+ well; 2 — interdevice n+-n+; 3 — intratransistor

(десятки пикосекунд), колцевые генераторы и блоки памяти ОЗУ.

В литературе достаточно широко освещена проблематика измерения кратковременных импульсов в логических элементах, предложены варианты тестовой обвязки [10, 11]. В отличие от логических элементов колцевой генератор не требует дополнительной тестовой обвязки. Одиночные импульсы напряжения от ТЧ исследуются по осциллограмме выходной частоты КГ, в котором от таких импульсов возникают функциональные сбои. СФ-блоки ОЗУ в данном случае не позволяют адекватно оценить их стойкость к одиночным импульсам напряжения, поскольку проявление такого эффекта сильно зависит от циклов обращения к блоку и частоты этих циклов.

При уменьшении проектных норм и увеличении быстродействия транзисторов чувствительность микросхем к одиночным импульсам напряжения от ТЧ возрастает. Поэтому

is determined by the parametric failure of static consumption current. The static consumption current is an additive value which is composed of the leakage currents of separate transistors and structures. The transistor leakage current is further subdivided into the intrinsic leakage current and radiation-induced leakage current. The intrinsic leakage current is composed of the subthreshold leakage current and pn-junction leakage current. Nanometer transistors carry the gate leakage current and the leakage current induced by the potential at the drain as well [8].

The radiation-induced leakage current of n-MOS transistors is caused by the accumulation of the positive charge in STI oxide, triggering of parasitic n-MOS transistors and formation of parasitic leakage paths which are classified into the interdevice and intratransistor ones in the general case. Figure 2 demonstrates a cross section of CMOS structures of leakage paths. Figures 3 and 4 demonstrate

the leakage indicated at the level of library elements with different status of inputs and memory cells.

Accordingly, the radiation models of logic elements with different status of inputs and memory cells depending on the data written in the SRAM IP-block are created based on the dose examination of n+-n+ and n+-n-well structures and transistors in different modes under exposure to radiation [9]. Characterization files are formed for various levels of accumulated dose. This makes it possible to evaluate the level of dose hardness as early as at the stage of static timing analysis of the design.

At present the method is being validated for 90 nm technology. A set of comprehensive radiation tests at various temperatures and in various modes on several chips will allow evaluating the accuracy of this approach with due account of the manufacturing tolerance of device parameters.

### STRUCTURES AND BLOCKS FOR EXAMINING THE BULK RADIATION EFFECTS IN VLSI SOCS

Bulk radiation effects in VLSIs arise when massive particles enter active structures [6]. Single (SEU, SET) and multiple (MBU, MCU) effects in logic and memory elements as well as latch-up (latch-up, SEL) are of highest interest in terms of test chip examination.

An array of serially connected logic elements with the corresponding test environment makes it possible to examine the short voltage pulse (SET) arising when a massive particle enters digital elements. The test environment serves for measuring very short impulses (dozens of picoseconds), ring oscillators and SRAM memory blocks.

The topic of the short impulse measurement in logic elements is widely covered in the literature and some variants of the test harness are proposed [10, 11]. A ring oscillator does not

Рис. 4. Радиационные модели ячеек памяти с обозначением радиационно-индуцированных токов утечки: 1 — внутритеористорные, 2 — межприборные  $n^+-n$ -карман, 3 — межприборные  $n^+-n^+$ , «0», «1» — логические состояния при облучении

Fig. 4. Radiation models of memory cells with radiation-induced leakage currents indicated: 1 — interdevice  $n^+-n$ -well, 2 — interdevice  $n^+-n^+$ , 3 — intratransistor

актуальными становятся методы подавления таких эффектов при проектировании. Одним из наиболее эффективных среди них является выбор и оптимизация параметров логической цепи. Исследовать данный метод позволяют КГ, построенные на различных логических элементах, с разными коэффициентами нагрузки и мощности элементов.

Наиболее чувствительной к сбою от ТЧ является ячейка памяти, поскольку для ее переключения требуется минимальное количество избыточного заряда. Поэтому одиночные

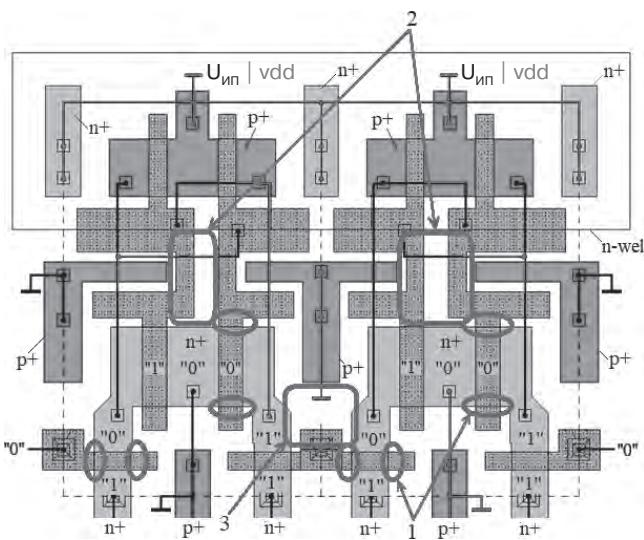

Рис. 5. Типовая структура для исследования ТЭ

Fig. 5. A typical structure for latch-up investigation

и многократные сбои исследуются только в блоках памяти с возможностью записи и считывания информации из накопителя для построения физической карты сбоев. При этом накопитель строится на ячейках памяти с различным конструктивно-топологическим исполнением для исследования эффективности соответствующих методов проектирования.

Исследовать проявление ТЭ при попадании ТЧ позволяют практически все предложенные тестовые элементы, однако наиболее простой среди них является типовая  $p-n-p-n$ -структура с привязкой  $n^+$  и  $p^+$ -областей к соответствующим потенциалам (рис. 5). Аналогичным по принципу построения тестовым элементом является массив ячеек памяти, который также позволяет оценить уровень стойкости к ТЭ и проанализировать различные конфигурации РС ячеек памяти, однако при этом является более показательным и наглядным.

## ЗАКЛЮЧЕНИЕ

Авторы считают, что в данной работе новыми являются следующие результаты.

require any additional test harness, unlike the logic elements. Single voltage impulses from the massive particle are studied using the oscillograph record of the output frequency of the ring oscillator, where such impulses cause functional failures. In this case SRAM IP-blocks do not ensure an adequate evaluation of their tolerance to single voltage impulses because the intensity of this effect depends to a large extent on the block access cycles and their dynamics.

Scaling down and speeding of transistors result in an increase in chip sensitivity to single voltage impulses from a massive particle. The methods for suppressing these effects at the design stage are therefore becoming important. One of the most efficient ones is the selection and optimization of logic circuit parameters. Ring oscillators with various load and power coefficients built using various logic elements make it possible to explore this method.

A memory cell is the most susceptible to a failure caused by a massive particle

because a minimum quantity of excess charge is enough to switch it. That is the reason why single and multiple failures are considered only in memory blocks with a capability of writing and reading the data from the storage circuit in order to build a physical failure map. In this regard the storage circuit is formed on the basis of memory cells with different constructive and topological design to investigate the efficiency of the corresponding design approaches.

Almost all proposed test elements allow examining latch-up in the presence of a massive particle. However, the simplest of them is a typical  $p-n-p-n$  structure with contacts of  $n^+$  and  $p^+$  regions to the corresponding potentials (Fig. 5). A memory cell array is implemented based on a similar concept; it allows evaluating the latch-up tolerance and analysing various configurations of radiation-hard memory cells, being at the same time more representative and illustrative.

## CONCLUSIONS

The authors consider the following results as novel:

1. The concept of the test chip, which implies developing a test chip for various purposes with the corresponding set of studies and requirements to the structures and blocks being examined.

2. The typical composition of the experimental test chip including structures and blocks for radiation tests. It has been demonstrated that the stage of development and examination of test chips is the key one in the VLSI design flow irrespective of its purpose.

3. The method of experiment-based calculation of VLSI dose hardness based on creating radiation models of standard digital elements and memory cells according to the results of radiation characteristic examination of the test structures and transistors on the test chip.

- Концепция создания ТК, которая предполагает разработку ТК для различных целей с соответствующим комплексом исследований и формированием требований к исследуемым структурам и блокам.

- Типовой состав экспериментального ТК, в который входят структуры и блоки для проведения радиационных испытаний. Показано, что этап разработки и исследования тестовых кристаллов является основным в маршруте проектирования СБИС независимо от его применения.

- Метод расчетно-экспериментальной оценки дозовой стойкости СБИС, основанный на создании радиационных моделей стандартных цифровых элементов и ячеек памяти по результатам радиационных исследований тестовых структур и транзисторов на ТК.

### ЛИТЕРАТУРА

- Lacoe R. C. *Improving Integrated Circuit Performance Through the Application of Hardness-by-Design Methodology*. IEEE Trans. Nucl. Sci. 2008. Vol. 55. P. 1903–1925.

- Московская Ю. М., Сорокуомов Г. С., Бобровский Д. В., Никифоров А. Ю., Денисов А. Н. и др. Рациональный состав типовой оценочной схемы для контроля радиационной стойкости партий пластин базовых матричных кристаллов // Проблемы разработки перспективных микро- и наноэлектронных систем — 2016. Сб. трудов / Под общ. ред. А. Л. Степковского. — М.: ИППМ РАН, 2016. — С. 153–157.

- Селецкий А. В., Шелепин Н. А., Смолин А. А., Уланова А. В. Исследование влияния разброса технологических параметров СБИС на стойкость к эффектам накопленной дозы радиации с помощью средств приборно-технологического моделирования // Проблемы разработки перспективных микро- и наноэлектронных систем — 2016. Сб. трудов / Под общ. ред. А. Л. Степковского. — М.: ИППМ РАН, 2016. — С. 178–183.

- Roche P., Gasiot G., Uznanski S., Daveau J. *et al. A Commercial 65 nm CMOS Technology for Space Applications: Heavy Ion, Proton and Gamma Test Results and Modeling*. IEEE Trans. Nucl. Sci. 2010. Vol. 57. P. 2079–2088.

- Герасимов Ю. М., Григорьев Н. Г., Кобыляцкий А. В., Меньшин Л. В., Петрикович Я. Я., Солохина Т. В. Среда проектирования быстродействующих радиационно-стойких КМОП СБИС СнК для космических систем по отечественным нанометровым технологиям объемного кремния // Электронная компонентная база космических систем, Сочи, 2017: материалы. — С. 31–32.

- Радиационная стойкость изделий ЭКБ: Научное издание / Под ред. А. И. Чумакова. — М: НИЯУ МИФИ, 2015.

- Петросянц К. О., Попов Д. А., Быков Д. В. TCAD-моделирование дозовых радиационных эффектов в суб100-нм high-k МОП-транзисторных структурах // Изв. вузов. Электроника. 2017. — Т. 22. — № 6. — С. 569–581.

- Barnaby H. J. *Total-Ionizing-Dose Effects in Modern CMOS Technologies*. IEEE Trans. Nucl. Sci. 2006. Vol. 53. P. 3103–3121.

- Герасимов Ю. М., Григорьев Н. Г., Кобыляцкий А. В., Петрикович Я. Я., Солохина Т. В. Перспективы создания быстродействующих радиационно-стойких КМОП СБИС СнК и ОЗУ по нанометровым технологиям объемного кремния // СВЧ-техника и телекоммуникационные технологии. — Севастополь, 2018: материалы. — С. 1–12.

- Ferlet Cavrois F., Pouget V., McMorrow D. *et al. Investigation of the Propagation Induced Pulse Broadening (PIPB) Effect on Single Event Transients in SOI and Bulk Inverter Chains*. IEEE Trans. Nucl. Sci. 2008. Vol. 55. P. 2842–2853.

- Dodd P., Shaneyfelt M. R., Felix J. A., Schwank R. J. *Production and Propagation of Single Event Transients in High-Speed Digital Logic IC*. IEEE Trans. Nucl. Sci. 2004. Vol. 51. P. 3278–3284.

### REFERENCES

- Lacoe R. C. *Improving Integrated Circuit Performance Through the Application of Hardness-by-Design Methodology*. IEEE Trans. Nucl. Sci. 2008. Vol. 55. P. 1903–1925.

- Moskovskaya Yu. M., Sorokoumov G. S., Bobrovskii D. V., Nikiforov A. Yu., Denisov A. N. i dr. *Ratsional'nyi sostav tipovoi otsenochnoi skhemy dlya kontrolya radiatsionnoi stoikosti partii plastin bazovyykh matrichnykh kristallov* // Problemy razrabotki perspektivnykh mikro- i nanoelektronnykh sistem — 2016. Sb. trudov / Pod obshch. red. A. L. Stempkovskogo. M.: IPPM RAN, 2016. P. 153–157. (In Russian).

- Seletskii A. V., Shelepin N. A., Smolin A. A., Ulanova A. V. *Issledovanie vliyaniya razbrosa tekhnologicheskikh parametrov SBIS na stoikost' k effektam nakoplennoi dozy radiatsii s pomoshch'yu sredstv priborno-tehnologicheskogo modelirovaniya* // Problemy razrabotki perspektivnykh mikro- i nanoelektronnykh sistem — 2016. Sb. trudov / Pod obshch. red. A. L. Stempkovskogo. M.: IPPM RAN, 2016. P. 178–183. (In Russian).

- Roche P., Gasiot G., Uznanski S., Daveau J. *et al. A Commercial 65 nm CMOS Technology for Space Applications: Heavy Ion, Proton and Gamma Test Results and Modeling*. IEEE Trans. Nucl. Sci. 2010. Vol. 57. P. 2079–2088.

- Gerasimov Yu. M., Grigor'ev N. G., Kobilyatskii A. V., Men'shenin L. V., Petrichkovich Ya. Ya., Solokhina T. V. *Sreda proektirovaniya bystrodeistvuyushchikh radiatsionno-stoikikh KMOPOB SBIS SnK i OZU po nanometrovym tekhnologiyam ob'emnogo kremniya* // SVCh-tehnika i telekommunikatsionnye tekhnologii. — Sevastopol', 2018: materialy. P. 1–12. (In Russian).

- Ferlet Cavrois F., Pouget V., McMorrow D. *et al. Investigation of the Propagation Induced Pulse Broadening (PIPB) Effect on Single Event Transients in SOI and Bulk Inverter Chains*. IEEE Trans. Nucl. Sci. 2008. Vol. 55. P. 2842–2853.

- Dodd P., Shaneyfelt M. R., Felix J. A., Schwank R. J. *Production and Propagation of Single Event Transients in High-Speed Digital Logic IC*. IEEE Trans. Nucl. Sci. 2004. Vol. 51. P. 3278–3284.