# НЕЙРОПРОЦЕССОР НА ОСНОВЕ КОМБИНИРОВАННОГО МЕМРИСТОРНО-ДИОДНОГО КРОССБАРА NEUROPROCESSOR BASED ON COMBINED MEMRISTOR-DIODE CROSSBAR

УДК 004.33; ВАК 05.27.01; DOI: 10.22184/1993-8578.2018.84.5.344.355

С.Удовиченко<sup>1</sup>, д.ф.-м.н.; А.Писарев<sup>1</sup>, к.т.н.; А.Бусыгин; О.Маевский<sup>2</sup>, к.т.н. / *udotgu@mail.ru*

*S.Udovichenko<sup>1</sup>, D.Sc.; A.Pisarev<sup>1</sup>, Ph.D.; A.Busygin; O.Maeovsky<sup>2</sup>, Ph.D.*

В работе представлена концепция автономного аппаратного средства – нейропроцессора, на котором могут базироваться как нейросети на простых нейронах, используемые в информационных технологиях, так и биоморфная нейросеть для моделирования работы кортикальной колонки человеческого мозга. Нейропроцессор как вычислительное устройство матрично-векторных операций включает в себя логическую и запоминающую матрицы, построенные на основе комбинированного мемристорно-диодного кроссбара. Предложены функциональная схема нейропроцессора, а также электрические схемы запоминающей матрицы и универсальной логической матрицы. Последняя в качестве программируемой логической матрицы выполняет умножение матрицы на вектор путем последовательных конъюнкций с инверсией; в качестве коммутатора направляет выходные импульсы нейронов на синапсы других нейронов; в качестве части входного устройства нейропроцессора реализует первичную обработку сигнала в цифровом режиме с помощью умножения матрицы на вектор, преобразуя входные данные в нужный формат; в качестве части выходного устройства осуществляет сжатие информации с помощью того же умножения для передачи в интерфейсный блок. Проведено SPICE-моделирование основных узлов нейропроцессора, показавшее высокую энергоэффективность предложенных матриц.

The paper presents the concept of an autonomous hardware – a neuroprocessor, on which both neural networks with simple neurons used in information technologies and a biomorphic neural network can be based for modeling the work of the cortical column of the human brain. Neuroprocessor as a computational device of matrix-vector operations includes logical and memory matrices based on a combined memristor-diode crossbar. We present a functional diagram of a neuroprocessor, electrical circuits of a storage matrix and a universal logical matrix. The latter as a programmable logical matrix performs matrix-vector multiplication by successive conjunctions with inversion; as a switch directs the output pulses of neurons to the synapses of other neurons; as part of the input device of the neuroprocessor implements the primary processing of the signal in the digital mode by multiplying the matrix by a vector, converting the input data into the desired format; as part of the output device, compresses the information with the same multiplication for transmission to the interface unit. SPICE-simulation of the main nodes of the neuroprocessor showed high energy efficiency of the proposed matrices.

<sup>1</sup> Тюменский государственный университет (625003, г. Тюмень, ул. Володарского, д. 6) / University of Tyumen (6 Volodarskogo St., 625003 Tyumen, Russia)

<sup>2</sup> ООО "Нанодевайсес" (Воронежская обл., Новоусманский р-н, пос. Отрадное, ул. Дачная, д. 46) / Nanodevices LTD (46, Dachnaya Str, Otradnoye, Novousmansky district, Voronezh region, 396335, Russia)

**И**скусственные нейронные сети появились как модель обработки информации в нейронах. Такой подход используется сейчас в системах машинного обучения с огромным числом простых нейронов. Концепция построения биоморфной модели нейрона, которая качественно отличается от формальной модели, и биоморфной нейросети на ее основе изложена в [1]. Одним из проектов масштабного моделирования нейросетей является Human Brain Project [2], ставящий целью полное моделирование работы мозга человека. Текущее развитие вычислительной техники не позволяет проводить подобные вычисления с приемлемой скоростью, поэтому пока исследователи ограничиваются отдельными функциональными участками. Особое внимание уделяется так называемой кортикальной колонке – универсальному элементу неокортекса [3, 4]. Именно эта структура считается элементарным модулем в системе обработки информации мозгом.

В настоящей работе представлена концепция автономного аппаратного средства – нейропроцессора, на котором могут базироваться как

нейросети на простых нейронах, используемые в информационных технологиях, так и биоморфная нейросеть для моделирования работы кортикальной колонки.

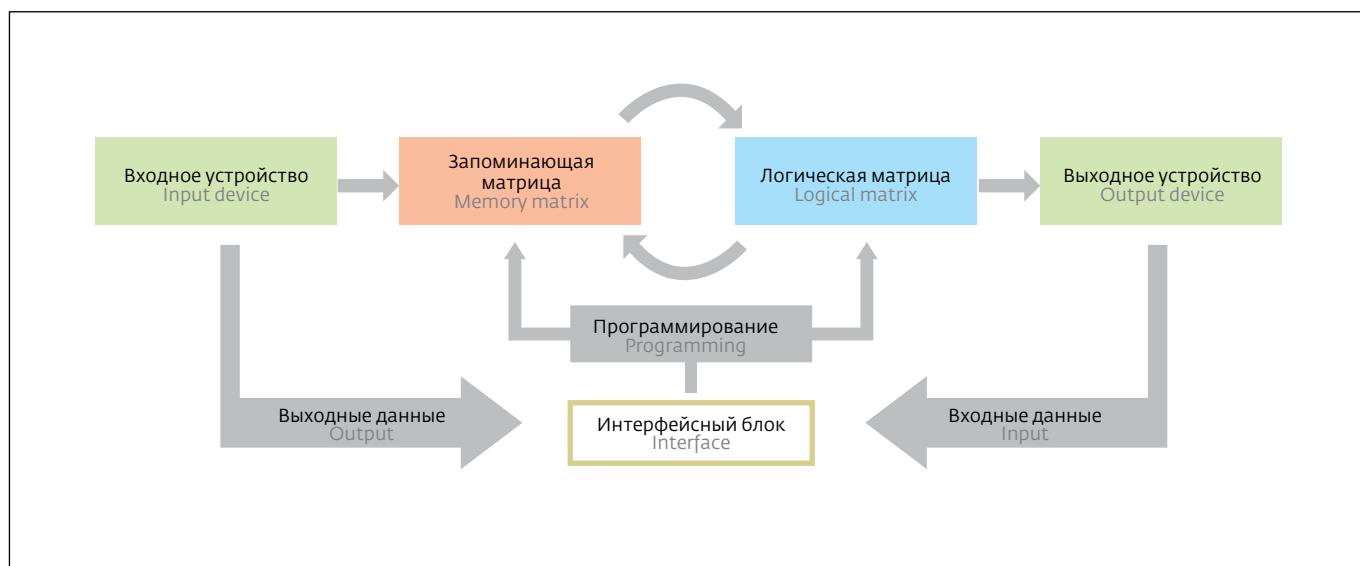

Функциональная схема нейропроцессора, в которую включены основные узлы, представлена на рис.1.

Входное устройство предназначено для первичной обработки аудио- и видеосигналов (преобразования данных, поступающих из интерфейсного блока, в нужный формат), а также для кодировки любой другой информации в виде отдельных импульсов и, если требуется, для преобразования этих импульсов в стандартные импульсы с определенными амплитудой и длительностью, подобные биоморфным импульсам мозга.

Запоминающая матрица помимо хранения информации проводит часть операций обработки для нейросети, выполняя взвешенное суммирование входных импульсов путем умножения напряжения входного сигнала на сопротивление согласно закону Ома и суммирования получившихся токов по первому закону Кирхгофа.

**A**rtificial neural networks appeared as a model for processing information in neurons. This approach is now used in machine learning systems with a huge number of simple neurons. The concept of designing a biomorphic model of a neuron, which qualitatively differs from the formal model, and a biomorphic neural network based on it, is presented in [1]. One of the projects of large-scale simulation of neural networks is the Human Brain Project [2], which aims to fully simulate the work of the human brain. The current development of computer technology does not allow such calculations to be carried out at an acceptable rate, and so far researchers are confined to separate functional areas. Particular attention is paid to the so-called cortical column – the universal element

of the neocortex [3, 4]. It is this structure that is considered as an elementary module in the brain information processing system.

This paper presents the concept of an autonomous hardware – a neuroprocessor, on which both a neural networks on simple neurons used in information technologies and a biomorphic neural network can be based to simulate the work of a cortical column.

The functional scheme of the neuroprocessor, which includes the main nodes, is shown in Fig.1.

The input device is intended for primary processing of audio and video signals (for converting data obtained from the interface unit to the desired format), as well as for encoding any other information in the form of separate pulses and, if necessary, to convert these pulses into standard

pulses with certain amplitudes and duration, similar to biomorphic impulses of the brain.

The storage matrix, in addition to storing information, performs a part of the processing operations for the neural network, performing a weighted summation of the input pulses by multiplying the voltage of the input signal by the resistance according to Ohm's law and summing the resulting currents according to the Kirchhoff's first law. The logical matrix simultaneously processes the digitized output pulses of the neurons of the memory matrix and commutes them to the synapses of other neurons. In this matrix, in addition to performing logical operations, the neural network problem of comparing the sum of signals with the threshold can be solved.

Рис.1. Функциональная схема нейропроцессора

Fig.1. Functional diagram of neuromodulator

Логическая матрица осуществляет одновременно обработку оцифрованных выходных импульсов нейронов запоминающей матрицы и их коммутацию на синапсы других нейронов. В этой матрице кроме выполнения логических операций может решатьсяся нейросетевая задача сравнения суммы сигналов с порогом.

Полная работа нейросети реализуется при соединении выходов логической и входов запоминающей матриц. Таким образом, нейроны из запоминающей матрицы можно объединить

в единую сеть с помощью логической матрицы. Логическое устройство должно выполнять умножение матрицы состояния ключей на вектор входных сигналов, обеспечивая коммутацию сигналов запоминающей матрицы. Поскольку такое умножение используется при обработке сигналов с помощью преобразования Фурье, то подобная матрица станет универсальной.

По окончании процессинга в запоминающей и логической матрицах, имеющих обратную положительную связь, и получения новых

The full operation of the neural network is realized when the outputs of the logical and inputs of memory matrix are connected. Thus, neurons from the memory matrix can be combined into a single network using a logical matrix. The logical device must perform multiplication of the key state matrix by the vector of the input signals, providing switching of the signals of the memory matrix. Since this multiplication is used in signal processing with the help of the Fourier transform, such a matrix will become universal.

At the end of processing in the memory and logical matrices

having a positive feedback and of receiving new data, the information is fed to the output device, where its final processing takes place (spectral analysis, image compression and convolution filtering). Further, the information prepared for transportation is transmitted to the interface unit.

In view of the scale of the architecture of the neuromodulator and the large number of elements in the electrical circuit, the following general requirements are imposed on its nodes: high degree of integration of elements when combining them

into an extremely large matrix; minimization of the area occupied by the cell of the matrix on the chip; high speed and energy efficiency.

### 3D MEMORY ARRAY WITH HIGH INTEGRATION OF ELEMENTS

The storage matrix based on the crossbar of complementary memristors [5], in contrast to the memory matrices used in information technologies, in addition to information storage allows the weighing and summation of the voltages of the input signals passing through the memristors. However, it can not be used

данных информация поступает на выходное устройство, где происходит ее окончательная обработка (спектральный анализ, сжатие изображения и сверточная фильтрация). Далее подготовленная к транспортировке информация передается на интерфейсный блок.

Ввиду масштабности архитектуры нейропроцессора и большого количества элементов в электрической схеме, к его узлам предъявляются следующие общие требования: высокая степень интеграции элементов при объединении их в сверхбольшую матрицу; минимизация площади, которую занимает ячейка матрицы на кристалле; высокое быстродействие и энергоэффективность.

### 3D ЗАПОМИНАЮЩАЯ МАТРИЦА С ВЫСОКОЙ ИНТЕГРАЦИЕЙ ЭЛЕМЕНТОВ

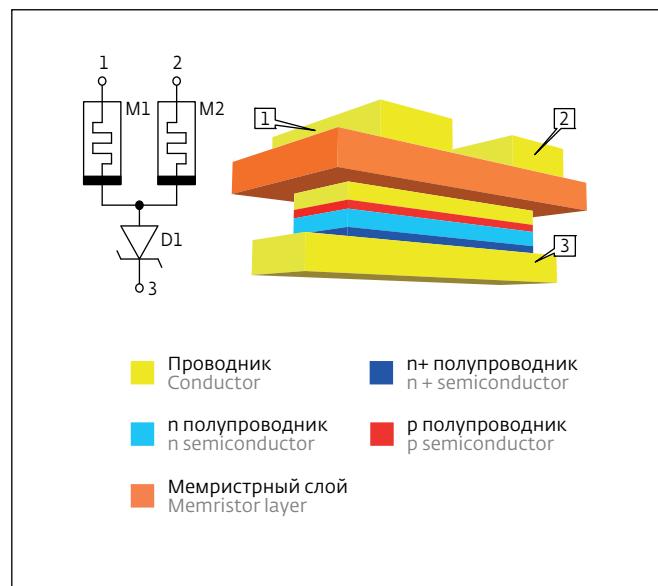

Запоминающая матрица на основе кроссбара из комплементарных мемристоров [5] в отличие от запоминающих матриц, используемых в информационных технологиях, помимо хранения информации позволяет производить взвешивание и суммирование напряжений входных сигналов, проходящих через мемристоры. Однако она не может быть использована в качестве сверхбольшой запоминающей матрицы нейропроцессора из-за низкой энергоэффективности при записи и высокой деградации выходного сигнала при считывании вследствие того, что в запоминающей ячейке отсутствует нелинейный селективный элемент.

as an ultra-large memory matrix of the neuroprocessor because of low energy efficiency during recording and high degradation of the output signal during reading because there is no nonlinear selective element in the storage cell.

The problem of energy efficiency of an ultra-large memory matrix is solved by using a complementary memristor-diode cell, which is a two-layered interconnection of complementary bipolar memristors and one Zener separating diode. The latter allows to reduce the degradation of the output signal

when summing the input voltage pulses.

The paper [6] presents nanotechnology for the manufacture of a superlarge (more than 10<sup>6</sup> cells) multilayer storage array with non-volatile memory and a high degree of integration of elements based on a combined memristor-diode crossbar.

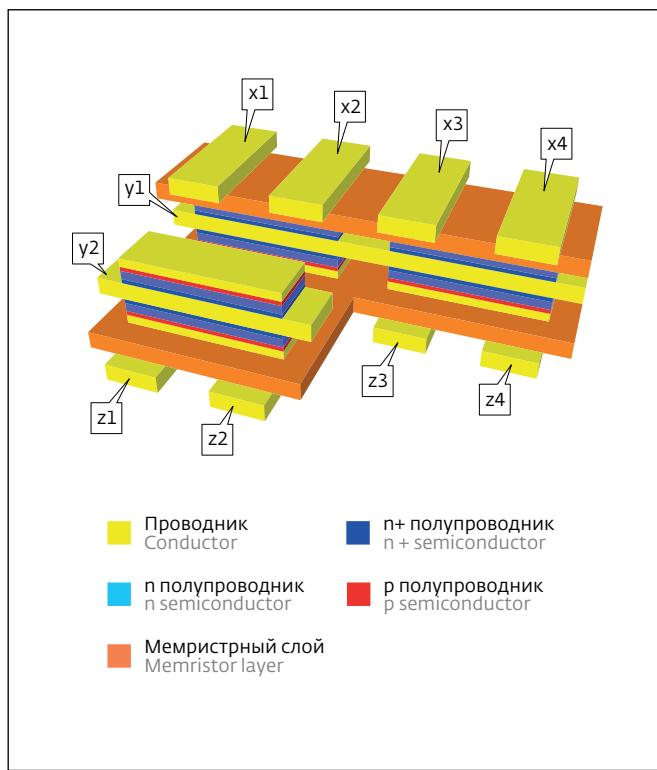

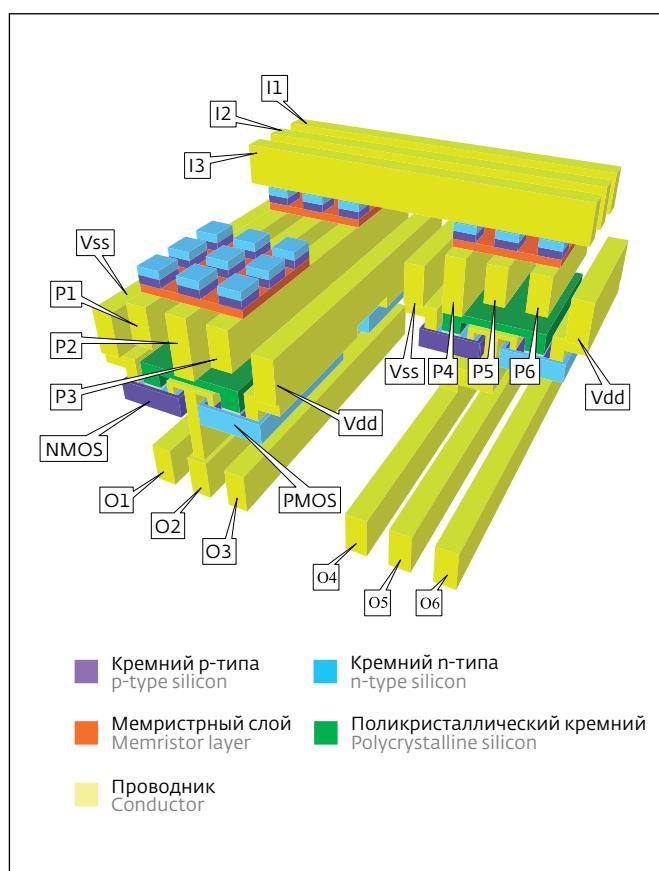

Technologically high degree of integration of elements can be achieved by sequential vertical build-up on a chip of planar two-layer memory matrices in a 3D structure of identical horizontally arranged and mirror-oriented combined crossbars (Fig.2).

Рис.2. Электрическая схема и топология отдельной ячейки кроссбара

Fig.2. Electrical diagram and topology of separate crossbar cell

Проблема энергоэффективности сверхбольшой запоминающей матрицы решена путем использования комплементарной мемристорно-диодной ячейки, которая представляет собой двухслойное соединение комплементарных биполярных мемристоров и одного разделяющего диода Зенера. Применение последнего позволяет уменьшить деградацию выходного

Due to the shortening of the length of the connecting conductors, the energy efficiency of the matrix is increased.

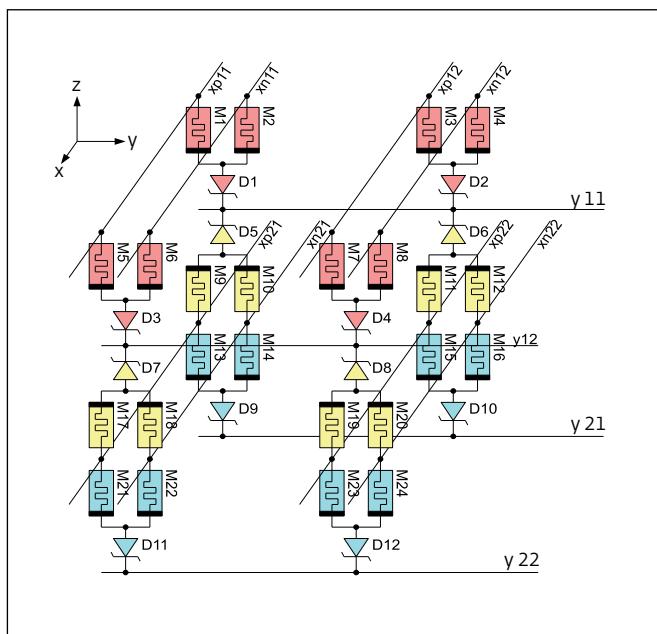

Two-layer combined crossbar can be considered as a separate functional layer. Fig.3 shows the electrical circuit, and Fig.4 presents the topology of the fragment of the three-dimensional memory matrix of the three combined crossbars explaining the principle of joining adjacent layers.

The memristor layer and semiconductor layers of the diode can be formed by a magnetron method. The layers of semiconductors with a donor or acceptor

Рис.3. Электрическая схема фрагмента трехмерной запоминающей матрицы. Три цвета соответствуют трем комбинированным кроссбарам

Fig.3. Electrical diagram of fragment of 3D memory matrix. Three colors correspond to three combined crossbars

сигнала при суммировании входных импульсов напряжения.

В [6] представлена нанотехнология изготовления сверхбольшой (более  $10^6$  ячеек) многослойной запоминающей матрицы с энергонезависимой памятью и высокой степенью интеграции элементов на основе комбинированного мемристорно-диодного кросбара.

Технологически высокая степень интеграции элементов может быть достигнута путем последовательного вертикального наращивания (sequential vertical build-up) на кристалле планарных двухслойных запоминающих матриц в 3D-структуре из одинаковых горизонтально расположенных и зеркально ориентированных по отношению друг к другу комбинированных кросбаров (рис.2). При этом благодаря сокращению длины соединительных проводников повышается энергоэффективность матрицы.

Двухслойный комбинированный кросбар можно рассматривать как отдельный функциональный пласт. На рис.3 приведена электрическая схема, а на рис.4 – топология фрагмента трехмерной запоминающей матрицы из трех комбинированных кросбаров, поясняющая принцип соединения соседних пластов.

Рис.4. Топология 3D запоминающей матрицы с высокой интеграцией элементов

Fig.4. Topology of 3D memory matrix with high integration of elements

Мемристорный слой и полупроводниковые слои диода могут быть сформированы магнетронным способом. Слои полупроводников с донорной или акцепторной примесью и разным уровнем легирования создаются путем одновременного распыления катодов из чистого полупроводника и легирующей примеси [7].

### УНИВЕРСАЛЬНАЯ 3D ЛОГИЧЕСКАЯ МАТРИЦА С ВЫСОКОЙ ИНТЕГРАЦИЕЙ ЭЛЕМЕНТОВ

Массив Акерса на основе мемристоров [8] можно запрограммировать на выполнение любой логической функции. Однако в одном массиве невозможно реализовать комбинационную схему умножения вектора на матрицу из-за наличия в нем только одного выхода. Использование нескольких массивов для организации такой операции приведет к росту количества элементов и, соответственно, к увеличению размеров логического устройства. При этом мемристорный массив Акерса обладает слабой интеграцией элементов, что связано с большим количеством транзисторов в ячейке, и высокой деградацией выходного сигнала при большом размере

матрицы. Если же использовать массив Акерса в последовательностной схеме, то снизится быстродействие из-за последовательного вычисления каждого разряда выходного вектора.

Планарная матрица Hewlett-Packard (HP) [9], предназначенная для обработки видеосигналов, выполняет умножение вектора на матрицу в аналоговом виде. Она может работать как цифровая логическая матрица при подаче входных логических сигналов на затворы транзисторов. Но и эта матрица не может использоваться в качестве логической сверхбольшой матрицы нейропроцессора из-за низкой интеграции элементов: на один транзистор с минимальным размером  $4F^2$  приходится лишь один мемристор размером  $1F^2$ . Эту матрицу не целесообразно использовать и в качестве входного устройства нейропроцессора, поскольку при сверхбольшом размере ее энергоэффективность крайне мала.

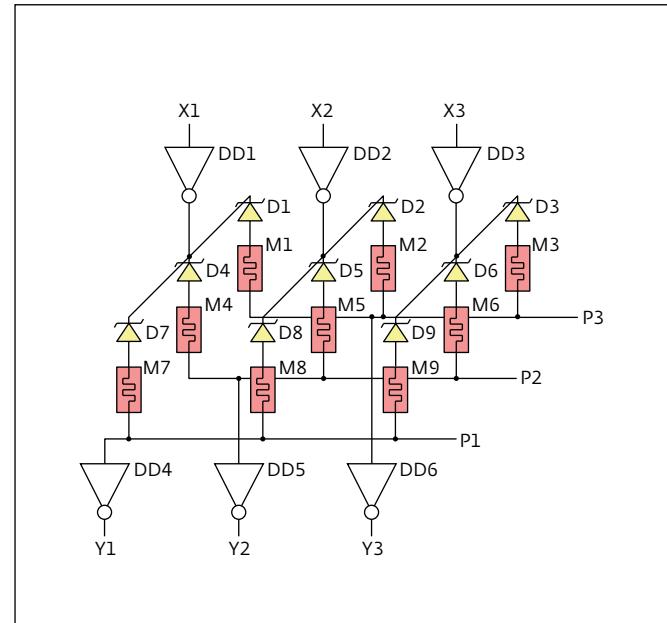

В [6] представлена нанотехнология изготовления сверхбольшой 3D логической матрицы с использованием логических вентилей и мемристорных коммутаторов, обладающей высокой степенью интеграции элементов. Электрическая схема элементарной ячейки логической матрицы, показанная на рис.5, представляет собой объединение мемристоров с селективными диодами Зенера, подключенное к одному из проводников кроссбара. В свою очередь этот проводник соединен с затвором КМОП-инвертора. Диод является частью логической цепи, а также устраняет паразитные токи при записи.

impurity and different levels of doping are created by the simultaneous sputtering of cathodes from a pure semiconductor and a dopant [7].

### UNIVERSAL 3D LOGICAL MATRIX WITH HIGH INTEGRATION OF ELEMENTS

The Akers logic array based on memristors [8] can be programmed to perform any logical function. However, in one array it is impossible to implement a combinatorial scheme for multiplying a vector by a matrix because there is only one output in it. Using multiple arrays to

organize such an operation will lead to an increase in the number of elements and, correspondingly, to an increase in the size of the logical device. At the same Akers logic array has weak integration of elements, which is connected with a large number of transistors in the cell and high degradation of the output signal at a large matrix size. If you use the Akers array in a sequential scheme, then the performance will decrease due to the sequential calculation of each digit of the output vector.

The Hewlett-Packard (HP) planar matrix [9], designed for

Рис.5. Электрическая схема функционального пластика с тремя ячейками и межпластовое соединение ячеек в логической матрице

Fig.5. Electrical diagram of a functional layer with three cells and interlayer coupling of cells in logical matrix

Комбинированный мемристорно-диодный кроссбар изготавливается по той же вакуумной нанотехнологии, что и кроссбар запоминающей матрицы, в производстве транзисторов КМОП-инвертора также используется известная нанотехнология.

processing video signals multiplies the vector by a matrix in analog form. It can work as a digital logical matrix when input logic signals to the gates of transistors. But even this matrix can not be used as a logical super-large matrix of a neuromodulator because of the low integration of elements: one transistor with a minimum size of  $4F^2$  has only one memristor of  $1F^2$  size. This matrix is not advisable to use also as an input device of a neuromodulator, since at an extremely large size its energy efficiency is extremely small.

Рис.6. Топология 3D логической матрицы с высокой интеграцией элементов: I, P – проводники кроссбара верхнего пласта; O – проводники нижнего пласта

Fig.6. Topology of 3D logical matrix with high integration of elements: I, P – conductors of the crossbar of upper layer; O – conductors of lower layer

In [6], nanotechnology for the manufacture of an extremely large 3D logical matrix using logic gates and memristor switches with a high degree of integration of elements is presented. The electrical circuit of the cell of the logical matrix shown in Fig.5 is a combination of memristors with selective Zener diodes connected to one of the crossbar conductors. In turn, this conductor is connected to the gate of the CMOS inverter. The diode is part of the logic circuit, and also eliminates spurious currents during recording.

The combined memristor-diode crossbar is manufactured using the same vacuum nanotechnology as the crossbar of the memory matrix, while the known nanotechnology is also used in the manufacture of CMOS-inverter transistors.

A single functional layer is created on the chip, containing CMOS inverters in the lower layer and a combined memristor-diode crossbar in the upper layer. The outermost layer is oriented orthogonally to the lower one, which is a necessary condition for the formation of commutating memristor crossbars between

На кристалле создается один функциональный пласт, содержащий в нижнем слое КМОП-инверторы, а в верхнем – комбинированный мемристорно-диодный кроссбар. Вышележащий пласт ориентирован ортогонально к нижнему, что является необходимым условием для образования коммутирующих мемристорных кроссбаров между пластами (рис.6). Такая конфигурация пластов является оптимальной, поскольку позволяет использовать выходные шины пласта в качестве проводников кроссбара. Число мемристоров, электрически соединенных с одним инвертором, равно числу синапсов (связей) одного нейрона в запоминающей матрице.

### SPICE – МОДЕЛИРОВАНИЕ РАБОТЫ ЗАПОМИНАЮЩЕЙ И ЛОГИЧЕСКОЙ МАТРИЦ

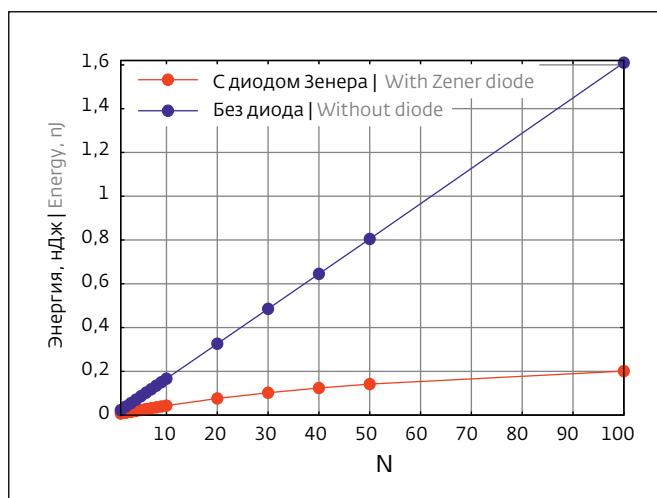

Моделирование работы матрицы выполнено в программе LTSpice версии XVII. Процесс записи в выбранную ячейку запоминающей матрицы происходит при последовательном изменении сопротивления ее мемристоров. Диод Зенера выступает в качестве селективного элемента и предотвращает паразитную запись в соседние ячейки кроссбара через смежные шины. Для исключения этой паразитной записи в матрице без диодов [5] на незадействованные шины подается половина напряжения записи, что приводит к увеличению энергопотребления.

Как видно из рис.7, затраты энергии на запись одной ячейки из комплементарных мемристоров в матрице размером 100×100 снижаются в 8 раз при добавлении в каждую ячейку диода

the layers (Fig.6). This configuration of the layers is optimal, since it allows the use of output buses of the layer as conductors of the crossbar. The number of memristors electrically connected to one inverter is equal to the number of synapses (bonds) of one neuron in the memory matrix.

### SPICE MODELING OF MEMORY AND LOGICAL MATRICES

Modeling of the matrix is performed in LTSpice version XVII. The process of recording to the selected cell of the memory matrix occurs with a consequent change in the resistance

Рис.7. Затраты энергии на запись одной ячейки комплементарных мемристоров без диода (синий цвет) и с диодом Зенера (красный цвет) в зависимости от числа ячеек в квадратной запоминающей матрице NxN

Fig.7. Energy required to write one cell of complementary memristors without a diode (blue) and with a Zener diode (red), depending on number of cells in square NxN memory matrix

Зенера. В обоих вариантах использовались худшие возможные условия для записи, при которых все ячейки матрицы изначально находились в одинаковом состоянии, а отношение сопротивлений мемристора в высокооомном и низкооомном состояниях  $R = (R_{\text{off}} - R_{\text{on}})/R_{\text{on}} = 10$ .

В сверхбольшой матрице, предложенной в настоящей работе, производится взвешивание

of its memristors. The Zener diode acts as a selective element and prevents parasitic recording into adjacent crossbar cells via adjacent buses. To eliminate this parasitic record in the matrix without diodes [5], half of the write voltage is applied to the unused buses, which leads to an increase in power consumption.

As can be seen from Fig.7, the energy costs for recording one cell of complementary memristors in a  $100 \times 100$  matrix are reduced by a factor of 8 in case of addition of a Zener diode to each cell. In both cases, the worst possible

recording conditions were used, in which all cells of the matrix were initially in the same state, and the ratio of the memristor resistances in the high-impedance and low-resistance states is  $R = (R_{\text{off}} - R_{\text{on}})/R_{\text{on}} = 10$ .

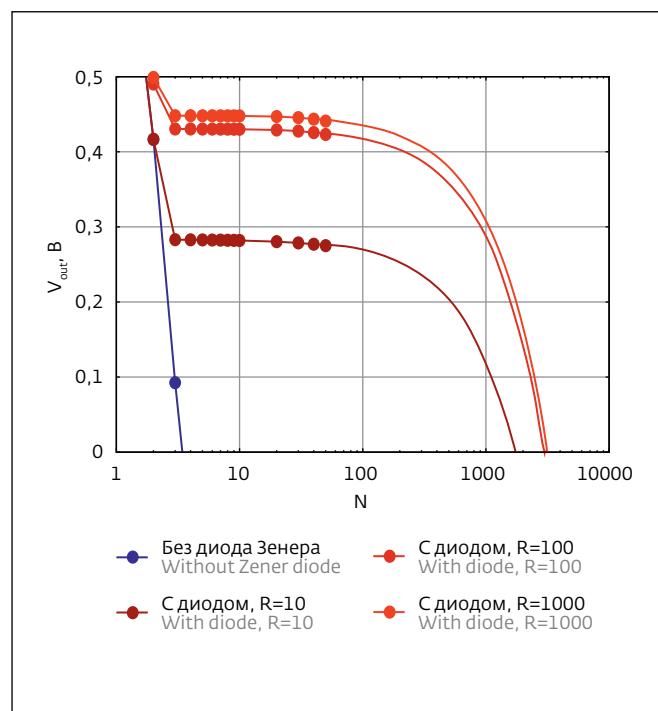

In the extremely large matrix proposed in this paper, we weigh and sum individual pulses. Work with individual input pulses can be considered as a sequential reading. Fig.8 shows the degradation of the output voltage as a function of the size of the square matrix  $N \times N$  with a single pulse of 1 V amplitude for three values of  $R$ : 10, 100 and 1000.

Рис.8. Зависимость выходного напряжения от размера запоминающей матрицы при последовательном чтении при разных R

Fig.8. Dependence of output voltage on size of memory matrix for sequential reading for different values of R

и суммирование отдельных импульсов. Работу с отдельными входными импульсами можно рассматривать как последовательное считывание. Рис.8 показывает деградацию выходного

Fig.8 shows that in the absence of a Zener diode in the cells, the output voltage decreases almost to zero already in the  $3 \times 3$  matrix. When the Zener diode is added, the output voltage decreases from 50% to 70% in a matrix of the same size, and a further increase in the size of the matrix has little effect on the magnitude of the output signal. A slowly varying output voltage level (about 0.3 V) is sufficient to perform a further summation procedure.

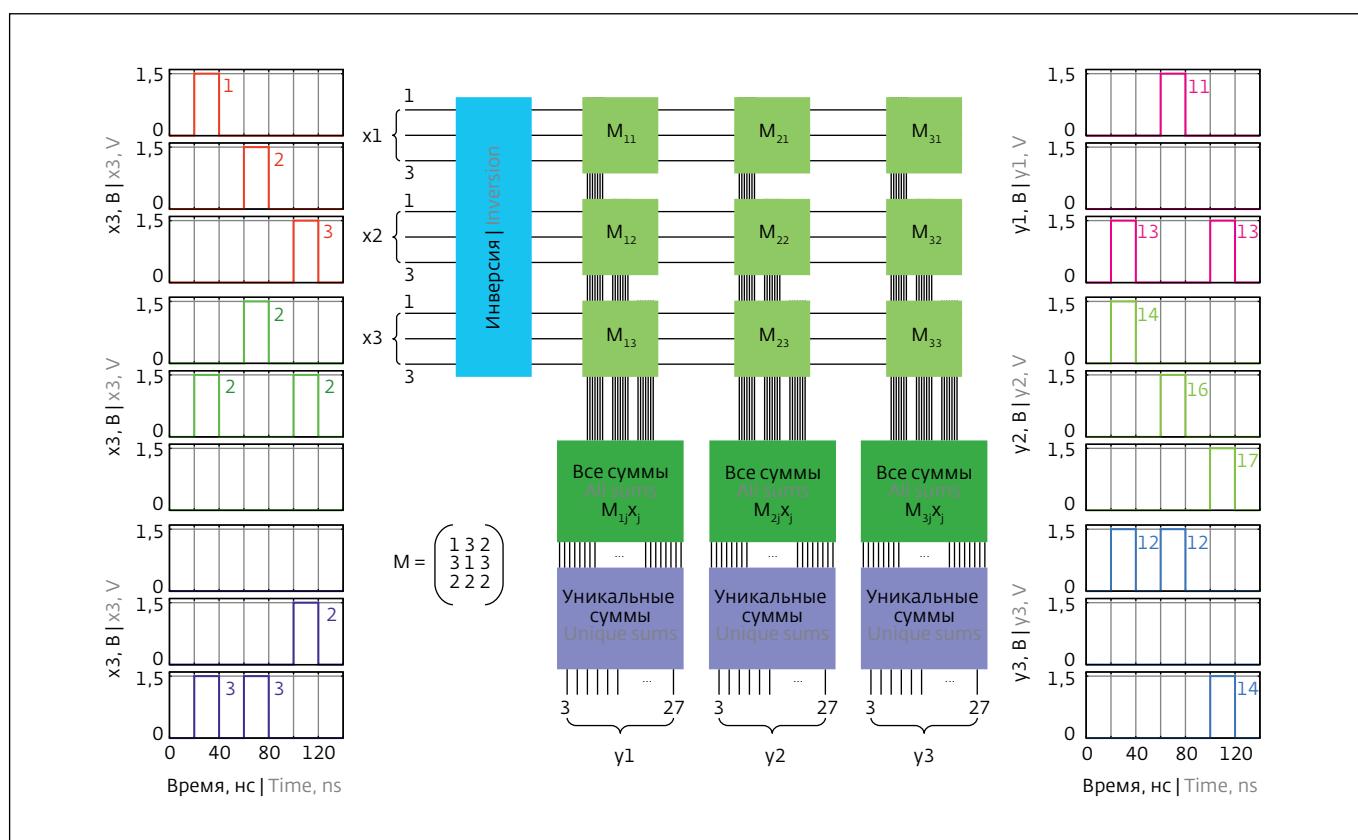

To model the operation of the universal logical matrix, a scheme was chosen (Fig.9), which performs the multiplication of

Рис.9. Моделирование умножения матрицы на вектор. Блоки разного цвета соответствуют разным функциональным пластам

Fig.9. Modeling of multiplication of matrix by vector. Blocks of different colors correspond to different functional layers

напряжения в зависимости от размера квадратной матрицы  $N \times N$  при подаче одного импульса амплитудой 1 В для трех значений R: 10, 100 и 1000.

Из рис.8 видно, что при отсутствии в ячейках диода Зенера выходное напряжение снижается практически до нуля уже в матрице 3×3. При

the 3×3 matrix by a vector of three components. Multiplication in several functional layers realizing a conjunction with inversion is possible when using positional number coding. Each input and output of the circuit is responsible for a particular numerical value. The blue block performs inversion of the input signals, light green - directly multiplication of the vector component by the matrix element by redirecting the pulse to the corresponding bus. The summation block consists of two parts: dark green blocks is a set of three-input AND-NOT elements corresponding to

the unique combinations (sums) of the products obtained, and the lilac blocks transmit unique sums to the output.

The proposed scheme is combinational and performs matrix-vector multiplication in one clock cycle.

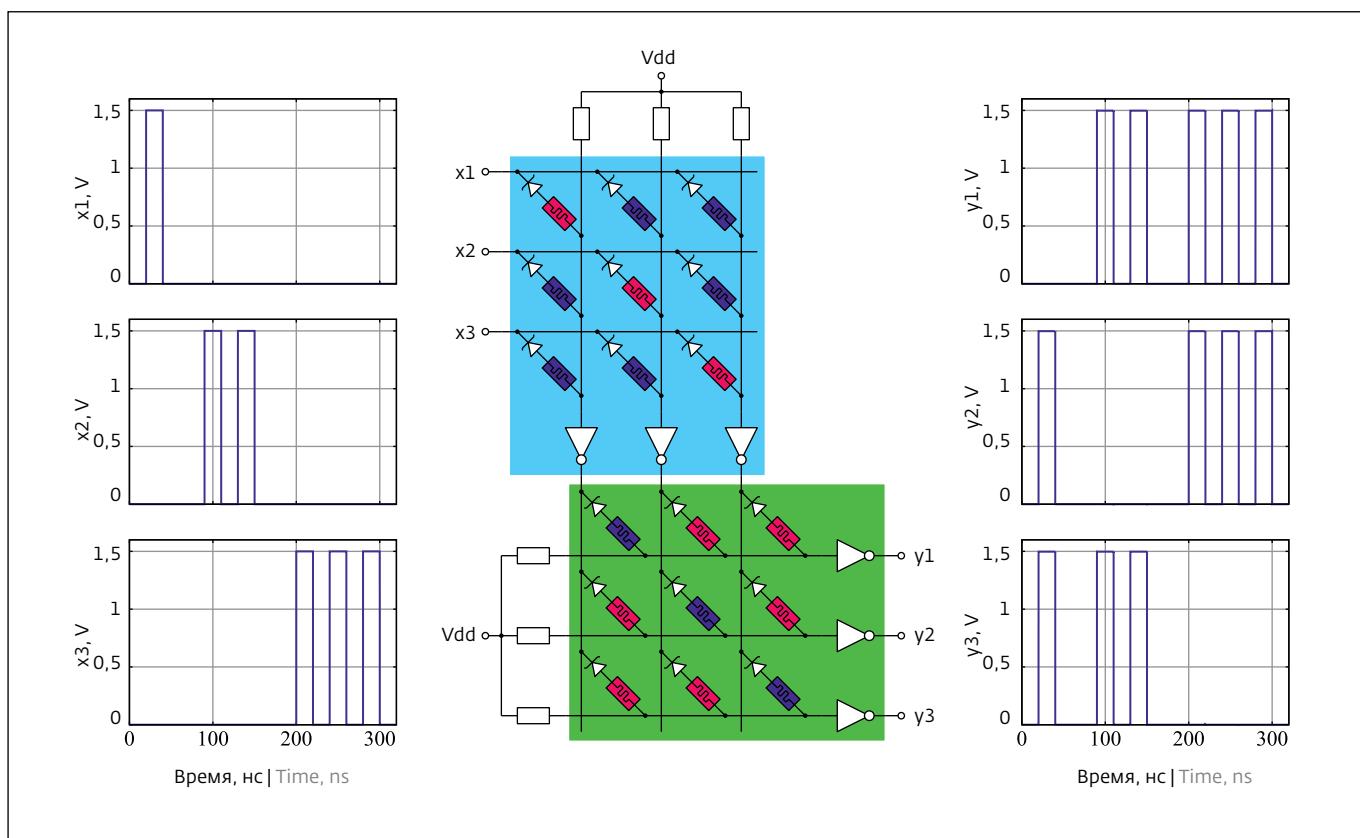

Fig.10 shows the switching of signals through different channels in a matrix of two functional layers. In the output of the first layer, inverted input signals are obtained, and the second layer performs their conjunction with inversion.

The matrix is programmed as follows: output y1 is connected

with inputs x2 and x3, output y2 - with x1 and x3, output y3 - with x1 and x2. The corresponding memristor conductivity are shown on the diagram in color: red means high conductivity, blue indicates low conductivity.

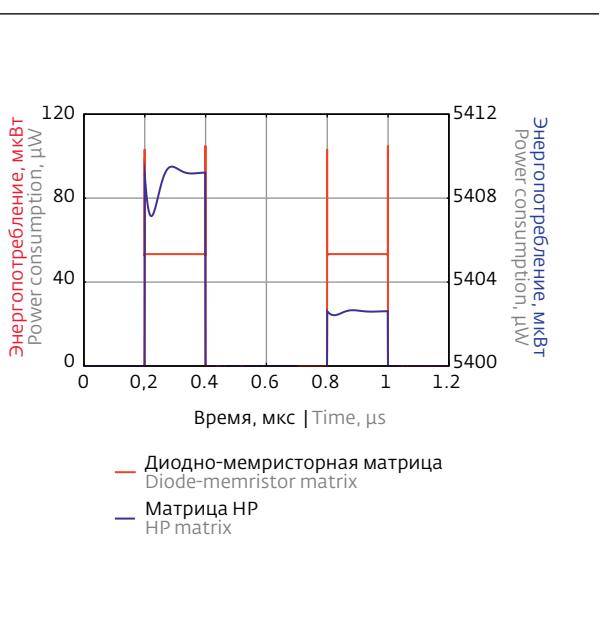

Fig.11 shows the time dependence of the power level consumed for processing the input signal with a diode-memristor matrix of 12×12 cells in binary code and four cells of the HP matrix [9] with a possible number of states equal to 64, which is equivalent to 6 bits. It follows from Fig.11 that the energy consumption (area under the curve)

Рис.10. Коммутация сигналов. Слева – входные, а справа – выходные сигналы. В середине синим цветом обозначен верхний пласт, зеленым – нижний пласт логической матрицы

Fig.10. Signal switching. On left are input, and on right are output signals. In middle, upper layer is marked in blue and lower layer of logical matrix is green

добавлении диода Зенера происходит снижение выходного напряжения в диапазоне от 50% до 70% в матрице того же размера, а дальнейшее увеличение размера матрицы слабо влияет на величину выходного сигнала. Медленно изменяющийся уровень выходного напряжения (около 0,3 В) достаточен для выполнения дальнейшей процедуры суммирования.

Для моделирования работы универсальной логической матрицы была выбрана схема (рис.9), выполняющая умножение матрицы  $3 \times 3$  на вектор из трех компонент. Умножение в нескольких функциональных пластиах, реализующих конъюнкцию с инверсией, возможно при использовании позиционного кодирования чисел. Каждый вход и выход схемы отвечает за конкретное числовое значение. Синий блок выполняет инверсию входных сигналов, светло-зеленый – непосредственно умножение компонента вектора на элемент матрицы путем перенаправления импульса на соответствующую шину. Блок суммирования состоит из двух частей: темно-зеленые блоки представляют собой набор

трехходовых элементов И-НЕ, соответствующих уникальным комбинациям (суммам) полученных произведений, а сиреневые блоки передают на выход уникальные суммы.

Предложенная схема является комбинационной и выполняет умножение матрицы на вектор за один такт.

На рис.10 показана коммутация сигналов по различным каналам в матрице из двух функциональных пластиах. На выходе первого пласта получаются инвертированные входные сигналы, а второй пласт выполняет их конъюнкцию с инверсией.

Матрица запрограммирована следующим образом: выход  $y_1$  скоммутируется со входами  $x_2$  и  $x_3$ , выход  $y_2$  – с  $x_1$  и  $x_3$ , выход  $y_3$  – с  $x_1$  и  $x_2$ . Соответствующие такой конфигурации проводимости мемристоров показаны на схеме цветом: красный обозначает высокую проводимость, синий – низкую.

На рис.11 представлена временная зависимость уровня мощности, потребляемой при обработке входного сигнала диодно-мемристорной

Рис.11. Изменение потребляемой мощности во времени: синий – матрица НР, красный – предлагаемая матрица

Fig.11. Change in power consumption over time: blue – HP matrix, red – suggested matrix

матрицей размером  $12 \times 12$  ячеек в двоичном коде и четырьмя ячейками матрицы НР [9] с возможным числом состояний равным 64, что эквивалентно 6 битам. Из рис.11 следует, что энергопотребление (площадь под кривой) диодно-мемристорной матрицы в 355 раз меньше, чем у матрицы НР. Основными потребителями энергии в матрице НР являются операционные

усилители (2,7 мВт на каждый ОУ), а в разработанной матрице – КМОП-инверторы, которые потребляют энергию в основном при переключениях. Таким образом, с увеличением числа ячеек разница в энергопотреблении этих матриц будет возрастать.

## CONCLUSION

The concept of hardware implementation of the neuroprocessor is presented and the main functional units of the device are

described. Both neural networks used in information technologies and a biomorphic neural network for modeling the work of the cortical column can be based on the neuroprocessor.

Electric diagrams of super-large 3D storage and logical matrices designed with the help of a combined memristor-diode crossbar, in which a high integration of elements have been achieved, are presented. The conducted SPICE-modeling showed high energy efficiency of these matrices.

The proposed logical matrix is universal. As a programmable

усилители (2,7 мВт на каждый ОУ), а в разработанной матрице – КМОП-инверторы, которые потребляют энергию в основном при переключениях. Таким образом, с увеличением числа ячеек разница в энергопотреблении этих матриц будет возрастать.

## ЗАКЛЮЧЕНИЕ

Представлена концепция аппаратной реализации нейропроцессора и описаны основные функциональные узлы устройства. На нейропроцессоре могут устанавливаться как нейросети, используемые в информационных технологиях, так и биоморфная нейросеть для моделирования работы кортикальной колонки.

Представлены электрические схемы сверхбольших 3D запоминающей и логической матриц, построенных с помощью комбинированного мемристорно-диодного кроссбара, в которых достигнута высокая интеграция элементов. Проведенное SPICE-моделирование показало высокую энергоэффективность этих матриц.

Предложенная логическая матрица является универсальной. В качестве программируемой логической матрицы она выполняет умножение матрицы на вектор путем последовательных конъюнкций с инверсией; в качестве коммутатора она направляет выходные импульсы нейронов на синапсы других нейронов; в качестве части входного устройства нейропроцессора реализует первичную обработку сигнала в цифровом режиме с помощью умножения матрицы

logical matrix, it performs matrix-vector multiplication by successive conjunctions with inversion; as a switch it directs the output pulses of neurons to the synapses of other neurons; as part of the input device of the neuroprocessor it performs the primary processing of the signal in the digital mode by multiplying the matrix by a vector, converting the input data into the desired format; as part of the output device it compresses the information with the same multiplication for transmission to the interface unit. ■

на вектор, преобразуя входные данные в нужный формат; в качестве части выходного устройства осуществляет сжатие информации с помощью того же умножения для передачи в интерфейсный блок.

#### ЛИТЕРАТУРА / REFERENCES

1. Filippov V.A. Chapter 5. Neuron modeling. In Aleksandrov Yu.I., Anokhin K.V., Bezdenezhnyh B.N. et al. Neuron. Signal Processing. Plasticity. Modeling. Fundamental Guide. - Publishing house of Tyumen State University, Tyumen, Russia, 2008, p. 468–535. Available at: [https://eknigi.org/nauka\\_i\\_ucheba/114893-nejron-obrabotka-signalov-plastichnost.html](https://eknigi.org/nauka_i_ucheba/114893-nejron-obrabotka-signalov-plastichnost.html) (accessed 30 July 2018).

2. Markham H. The Human Brain Project. – Scientific American, 2012, 306, № 6, p.50-55. doi: 10.1038/scientificamerican0612-50.

3. Silberberg G., Gupta A., Markram H. Stereotypy in neocortical microcircuits. TRENDS in Neurosciences, 2002, 25, № 5, p. 227-230. doi: 10.1016/S0166-2236(02)02151-3.

4. De Felipe J., Alonso-Nanclares L., Arellano J. Microstructure of the neocortex: Comparative aspects. Journal of Neurocytology, 2002, 31, p. 299-316. pmid: 12815249.

5. Bennet C., Querlioz D., Klein J. Spatio-temporal Learning with Arrays of Analog Nanosynapses, 2017 IEEE/ACM International Symposium on Nanoscale Architectures. doi: 10.1109/NANOARCH.2017.8053708.

6. Udovichenko S., Pisarev A., Busygin A., Maeovsky O. 3D CMOS memristor nanotechnology for creating logical and memory matrices of neuromprocessor. NANOINDUSTRY. 2017. № 5, P. 26-34. doi: 10.22184/1993-8578.2017.76.5.26.34.

7. Kim H.K., Li C.C., Fang X.M., Solomon J. et al. Erbium Doped Semiconductor Thin Films Prepared by RF Magnetron Sputtering. Materials Research Society Symposia Proceedings, 1993, 301, p. 55-60. doi: 10.1557/PROC-301-55.

8. Levy Y., Bruck J., Cassuto Y., Friedman E.G. et al. Logic operations in memory using a memristive Akers array. Microelectronics Journal, 2014, 45, p.1429-1437. doi: 10.1016/j.mejo.2014.06.006.

9. Li C., Hu M., Li Y., Jiang H. et al. Analogue signal and image processing with large memristor crossbars. Nature electronics, 2018, 1, № 1, p. 52-59. doi: 10.1038/s41928-017-0002-z.