УДК 621.391.31/621.382

DOI: 10.22184/NanoRus.2019.12.89.287.296

# МЕТОДИКА ОЦЕНКИ ВЕРОЯТНОСТИ ВОЗНИКНОВЕНИЯ БИТОВЫХ ОШИБОК В ПРИЕМОПЕРЕДАТЧИКАХ SpaceFibre

## ESTIMATING BER IN SpaceFibre TRANSCEIVERS

БАЙКОВ ВАЛЕРИЙ ДМИТРИЕВИЧ<sup>2</sup>ДОМОЖАКОВ ДЕНИС АЛЕКСАНДРОВИЧ<sup>1,2</sup>

DADomozhakov@mephi.ru

ДУБИНСКИЙ АЛЕКСЕЙ ВАСИЛЬЕВИЧ<sup>1,2</sup><sup>1</sup>АО «Научно-производственный центр «Электронные вычислительные-информационные системы»

124498, г. Москва, г. Зеленоград, проезд №4922, 4, стр. 2

<sup>2</sup>Национальный исследовательский

ядерный университет «МИФИ»

115409, Россия, г. Москва, Каширское ш., 31

BAYKOV VALERIY D.<sup>2</sup>DOMOZHAKOV DENIS A.<sup>1,2</sup>

DADomozhakov@mephi.ru

DUBINSKIY ALEXEY V.<sup>1,2</sup><sup>1</sup>R&D Center “ELVEES”, JSC

bld. 2, 4 Lane 4922, Zelenograd, Moscow, 124498, Russia

<sup>2</sup>National Research Nuclear University MEPhI,

31 Kashirskoe Highway, Moscow, 115409, Russia

В статье предложена методика оценки частоты возникновения битовых ошибок (BER) в мультискоростных приемопередатчиках последовательного канала на этапе проектирования. Приведена модель критичных узлов тракта передатчик—приемник.

**Ключевые слова:** BER; интерфейс; приемопередатчик; линия связи; последовательная передача данных; SERDES; восстановление тактового сигнала из данных.

The article considers a method for estimating bit error ratio (BER) in multispeed transceivers of the serial channel at the design stage. A model of critical nodes of the path has been given.

**Keywords:** BER; interface; transceiver; communication line; serial data transmission; SERDES; clock/data recovery.

### ВВЕДЕНИЕ

Функцию обмена данными между блоками внутри цифровой вычислительной системы выполняют приемопередатчики. Принцип их работы состоит в свертке поступающего на вход параллельного потока данных в последовательный, формированиям электрических уровней, соответствующих стандарту обмена, трансляции сигнала по линии передачи, его захвате приемником и развертке в параллельный поток данных, пригодный для последующей обработки.

В настоящее время активно развивается стандарт высокоскоростной последовательной и параллельной передачи данных SpaceFibre [1]. Данный стандарт включает в себя требования по проектированию высокоскоростных приемопередатчиков последовательного канала, предназначенных для обмена данными между устройствами в составе космических аппаратов и работающих на скоростях до 6,25 Гбит/с.

Одной из основных количественных характеристик, наглядно определяющих качество передачи цифровых данных, является частота возникновения битовых ошибок (в англоязычной литературе Bit Error Ratio или BER). В соответствии с требованиями к современным приемопередатчикам ответственного применения BER не должен превышать  $10^{-12}$ . В публикациях на тему разработки и измерения приемопередатчиков тематике BER уделяется много внимания. Прямой анализ при моделировании, аналогичный физическим измерениям по подсчету числа ошибок на этапе проектирования, требует до десятка часов. Использование приемов, сокращающих время тестирования, ухудшает точность результатов [2].

В настоящий момент получила широкое развитие теория джиттера как основной причины появления ошибок при передаче сигнала. Большое внимание уделяется физическому измерению BER разработанных образцов приемопередатчиков. Известны методики анализа джиттера передаваемого сигнала данных, разложение его на компоненты для последующего анализа работы приемопередающего тракта [3, 4]. Множество работ посвящено беспроводным интерфейсам, влиянию линии передачи, внутренним функциям тестирования, системам физического измерения BER готовой системы [5]. Также известны методики оценки BER, призванные сократить затрачиваемое на измерение время. Данные методики являются пригодными для развития подхода к предсказанию BER на этапе проектирования.

Предметом данного исследования являются развитие теории оценки частоты возникновения битовых ошибок в тракте последовательной передачи цифрового потока данных через проводную или оптическую среду на этапе проектирования и разработка универсальной методики построения высокоскоростных приемопередатчиков последовательного канала. Предлагаемая методика основана на оптимизации составляющих их блоков в целях минимизации частоты битовых ошибок. Объектом исследования являются критичные блоки в составе приемопередатчиков, функционирующие на частотах, равных и кратных частоте транслируемого битового потока данных.

Предложено усовершенствование статистической методики оценки BER [6]. Усовершенствование заключается в добавлении дополнительных параметров, характеризующих особенности строения и работы приемопередатчика (коэффициент передачи,

задержка, шум и т.д.). Методика BER основывается на математической модели приемопередающего тракта, включает контроль характеристик сигналов на входе элементов памяти приемника, выполняющих функцию первичной записи поступающих данных.

## ОСНОВНЫЕ ПОЛОЖЕНИЯ

В случае отсутствия функциональных нарушений работы исследуемого приемопередатчика, а также наличия достаточных запасов по быстродействию цифрового домена системы BER зависит от фазовых соотношений между цифровыми сигналами и тактовыми сигналами на входе триггеров, записывающих данные и производящих первичную десериализацию потока данных. Относительное расположение перепадов этих сигналов зависит во времени от джиттера.

Предлагается рассматривать джиттер тактового сигнала относительно неподвижного сигнала данных. При этом фазовые искажения, накопленные в процессе трансляции потока данных через тракт, преобразуются в джиттер тактового сигнала.

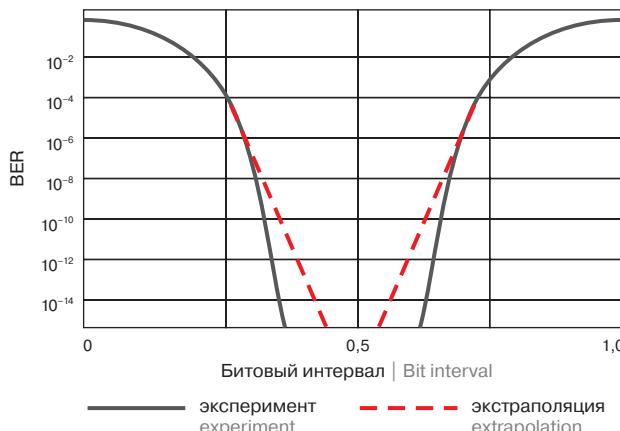

*Rис. 1. Появление ошибки при экстраполяции результатов*

*Fig. 1. An error occurring upon applying results extrapolation*

Накопление фазовых искажений производится в процессе формирования и следования потока данных через тракт приемопередатчика, а также его тактирования и захвата триггером приемника. Таким образом, модель оценки BER должна включать в себя описание устройства и принципов функционирования элементов приемопередатчика, от которых зависит результирующий джиттер.

## ВЫБОР МЕТОДА ОЦЕНКИ BER

Существуют подходы к оценке BER на этапе разработки, основанные на нескольких принципах. В качестве базы для развития представленной методики были рассмотрены следующие.

- Прямое моделирование в САПР. Данный подход позволяет, если в достаточной мере учтены ключевые факторы, получить величину BER с высокой точностью. Прямое моделирование отличается универсальностью и простотой реализации. Однако подобный цикл расчета может длиться от нескольких дней и дольше.

- Моделирование на наихудший случай. Представляет собой вариант прямого моделирования в САПР, при котором намеренно ухудшаются отдельные параметры модели, такие как отношение сигнал/шум, длина линии, джиттер тактовых сигналов. Это делает возможным снижение затрачиваемого времени на несколько порядков. Но вследствие появления ошибки экстраполяции (рис. 1) снижается точность расчета.

- Статистический метод. Основан на случайному характере фазового шума. Пригоден для создания универсальной модели тракта передачи данных, позволяющей на небольшое время провести комплексный анализ качества работы устройства. Параметры и характеристики разрабатываемого приемопередатчика транслируются в математическую модель. Сам расчет занимает минимальное время (до нескольких минут). Требуется охарактеризовать ключевые элементы тракта. Результат зависит от объема статистической выборки и точности результатов характеризации.

## INTRODUCTION

Transceivers perform data exchange among the blocks of a digital computing system. The principle of their operation consists in transforming the incoming parallel data stream into a serial one, forming electric levels compliant with the interchange standard, transmitting the signal along the transmission line, receiving the signal by the receiver and transforming it into a parallel data stream suitable for further processing.

SpaceFibre standard of high-speed serial and parallel data transmission is rapidly developing now [1]. This standard includes requirements for designing high-speed transceivers of the serial channel used to exchange data among devices being parts of spacecraft and operating at speeds of up to 6.25 Gbit/s.

Bit Error Ratio (BER) is one of the main quantity characteristics describing the quality of digital data transmission. According to the

requirements for state-of-the-art transceivers for demanding applications, BER should not exceed  $10^{-12}$ . The BER topic is widely discussed in the literature on transceiver development and measurement. In the process of simulation at the design stage, direct analysis similar to physical error counting requires up to ten hours. Techniques reducing the testing time compromise the accuracy of the results [2].

The theory of jitter as the main cause of errors occurring during signal transmission has become widespread recently. A lot of attention is paid to physical measurement of BER of the developed transceiver samples. There are methods of analysis of transmitted data signal jitter and its breakdown into components for further analysis of transceiver path functioning [3, 4]. There are a lot of works on wireless interfaces, transmission line influence, internal testing functions and

systems for physical BER measurement of the complete system [5]. There are BER evaluation methods aimed at reducing measurement time. These methods are suitable for developing an approach to BER forecasting at the design stage.

The subject-matter of this paper is development of a theory of evaluating of Bit Error Rate in the path of the serial digital data stream transmission through a hardware or optical medium at the design stage and development of a universal method of designing high-speed transceivers of the serial channel. The proposed method is based on optimizing the component blocks of the transceivers in order to minimize the Bit Error Rate. The authors have researched sensitive blocks that are part of transceivers, functioning at frequencies equal to or divisible by the frequency of the transmitted data bit stream.

- Использование высокоуровневых моделей. Позволяет заменить подробные модели отдельных блоков на упрощенные, что приводит к уменьшению требуемого времени. Требует построения дополнительных моделей, их характеристизации. Наиболее эффективным является расчет в специализированных САПР.

### СТАТИСТИЧЕСКИЙ ПОДХОД ПРИ ОЦЕНКЕ BER

За основу разработанной методики был взят статистический подход, поскольку он отличается высокой скоростью расчета, возможностью адаптации под множество архитектур приемо-передатчиков, чья математическая модель может быть расширена и усложнена. В этом случае повышение точности результата достигается в первую очередь путем усложнения алгоритма обработки данных, а не увеличения их объема, как при моделировании или измерениях готовых образцов.

Критерием принадлежности приемопередатчика определенному стандарту передачи является выполнение требований по соответствию глазковой диаграммы передаваемых данных маске, соответствующей наихудшему случаю электрических параметров и джиттера. При этом в роли параметра рассматривается величина суммарного джиттера, накопленного на протяжении определенного времени и при передаче определенного кода. При данном подходе джиттер зависит от передаваемой кодовой последовательности и от объема выборки. Данный метод позволяет провести первичную оценку качества работы тракта.

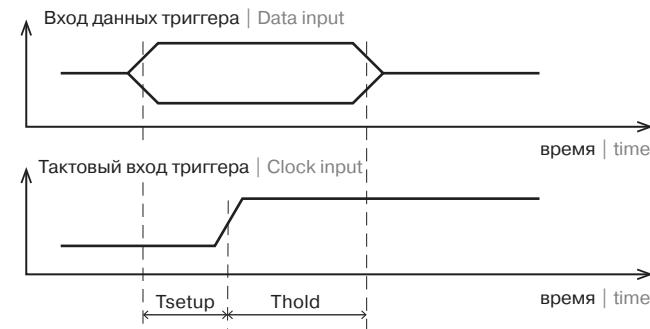

В рамках такой модели BER сильно зависит от взаимной фазы сигналов на входе элементов памяти первой ступени десериализации приемника. Необходимым условием получения приемником верных данных является соблюдение разрешенных временных соотношений между переключением сигнала данных и тактирующего сигнала на входе триггера в цифровой части приемника, как показано на рис. 2. Данные должны поступить на вход не позже, чем за минимальное время предустановки ( $T_{setup}$ ) до перепада тактирующего сигнала. Одновременно с этим данные должны оставаться на входе после перепада тактового

сигнала не менее, чем минимальное время удержания ( $Thold$ ). При невыполнении хотя бы одного из условий запись правильной информации считается невозможной.

В условиях наличия фазового шума возрастает вероятность появления ошибки при приеме в ситуации, когда или приход данных относительно переключения тактирующего сигнала осуществляется слишком поздно, или выставленные на входе данные удерживаются недостаточно долго.

Вероятностное распределение фронтов исследуемых сигналов описывается с помощью нормального распределения. Возникновение ошибки можно рассмотреть как одновременное наступление двух случайных событий, при которых не выполняется условие временных соотношений между приходом тактового сигнала и сигнала данных. Распределение плотности вероятности события, при котором не выполняется условие по минимальному  $T_{setup}$ , изображено на рис. 3.

В основе методики лежит принцип построения и использования статистической модели вероятности возникновения ошибки при передаче одного бита. Вначале выполняется анализ устройства тракта передачи и расчет джиттера отдельных блоков на пути следования сигнала. Полученный джиттер предлагается рассматривать как приведенный к джиттеру тактового сигнала

Рис. 2. Условия по взаимной фазе сигналов

Fig. 2. Conditions for the mutual signal phase

This paper proposes an improvement in the statistical method of BER evaluation [6]. The improvement consists in adding extra parameters specifying the structure and operation features of the transceiver (transmission factor, delay, noise, etc.). The BER method is based on the mathematical model of the transceiver path and implies monitoring of signal characteristics at the inputs of receiver memory elements which perform the initial writing of the incoming data.

### THESES

Providing that there are no functional failures in the operation of the transceiver being investigated and the digital domain of the system has enough operational speed margin, BER depends on the phase relationship between digital and clock signals at the input of the triggers which write data and perform the initial deserialization of the data stream.

The relative position of the edges of these signals depends on the jitter over time.

The paper proposes considering clock signal jitter relative to the fixed data signal. In such a case the phase distortions accumulated during data stream transmission through the path will transform into clock signal jitter.

Phase distortions are accumulated in the process of data stream formation and passage through the transceiver path as well as its clocking and receiving by the receiver trigger. Consequently, the BER evaluation model should include the description of the device and the operating principles of the transceiver module elements which determine the resulting jitter.

### SELECTING A BER EVALUATION METHOD

There are several approaches to BER evaluation at the design stage, which are

based on several principles. The following approaches have been considered as a basis for the proposed method:

- Direct simulation in CAD systems. If the key factors are taken into account properly enough, this approach produces a highly accurate BER value. The distinctive features of direct simulation are its versatility and simplicity of implementation. However a calculation cycle of that kind may take several days or longer.

- Worst-case simulation. This simulation is a variation of direct simulation in CAD systems, whereby some characteristics of the model, such as signal/noise ratio, line length, and clock signal jitter, are intentionally worsened. This makes it possible to decrease the calculation time by several orders of magnitude. However, this reduces the accuracy of the calculation because of the extrapolation error (Fig. 1).

Рис. 3. Распределение вероятности прихода передних фронтов сигналов

Fig. 3. The probability distribution of the rising edge arrival

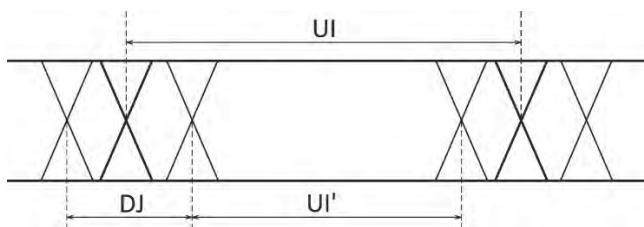

Рис. 4. Уменьшение битового интервала

Fig. 4. Bit interval reduction

относительно принимаемого потока данных на входе элементов памяти первой ступени десериализации приемника. Далее производится построение распределения плотностей вероятностей нарушения требований по минимальным временам предустановки и удержания сигнала данных при его записи (1):

$$DPC = \frac{1}{\sigma \sqrt{2\pi}} e^{\frac{(x-m)^2}{2\sigma^2}}, \quad (1)$$

где  $\sigma$  — СКО распределения момента перепада уровня тактового сигнала внутри битового интервала,  $x$  — текущее значение

момента перепада тактового сигнала,  $m$  — математическое ожидание момента перепада.

Заключительный этап расчета BER заключается в интегрировании полученного распределения на интервалах, соответствующих появлению битовой ошибки (2):

$$BER = 1 - \int_0^{UI} DPC(t) dt, \quad (2)$$

где  $UI$  — битовый интервал сигнала данных.

Данный подход делает возможным расчет вероятности битовых ошибок за относительно малое время. Однако точность полученного результата сильно зависит от соответствия модели разрабатываемому устройству. В следующем разделе освещены положения, позволяющие существенно повысить точность расчета.

## МЕТОДИКА ОЦЕНКИ BER

Элементы тракта передачи данных могут генерировать как случайный, так и детерминированный джиттер. Случайный джиттер ( $RJ$ ) имеет природу шума, что делает возможным его описание с помощью нормального закона распределения момента перепада сигнала. Параметрами в данном случае являются математическое ожидание и среднеквадратичное отклонение.  $RJ$  тактовых сигналов и данных приводятся к джиттеру тактового сигнала относительно битового интервала данных. Детерминированный джиттер ( $DJ$ ) ограничен сверху максимальным значением. Следствием воздействия  $DJ$  высокой частоты является уменьшение битового интервала. Уменьшение битового интервала при появлении детерминированного джиттера высокой частоты проиллюстрировано на рис. 4.

Таким образом, при интегрировании плотности распределения вероятностей формула (2) преобразуется в формулу (3):

$$BER = 1 - \int_{(DJ/2)+T_{setup,\min}}^{UI-(DJ/2)-T_{hold,\min}} DPC(t) dt. \quad (3)$$

Составляющими детерминированного джиттера являются:

- функциональный джиттер ФАПЧ передатчика  $DJ_{PLL}$ ;

- Statistical method. It relies on the random nature of the phase noise. This method is suitable for creating a universal model of the data transmission path allowing integrated analysis of the device performance within a short period of time. The parameters and characteristics of the developed transceiver module are transferred into a mathematical model. The calculation itself takes minimum time (up to several minutes). It is required to characterize the key elements of the path. The result depends on the statistical sampling size and the accuracy of characterization results.

- Using high-level models. This method allows replacing detailed models of separate blocks by the simplified ones, which reduces the required calculation time. The method involves generation of additional models and their characterization.

Calculation in specialized CAD systems is the most efficient.

## THE STATISTICAL APPROACH TO BER EVALUATION

The statistical approach has been used as a basis for the proposed method because it is characterized by a high calculation speed and is adaptable to many transceiver architectures with a possibly expanded and more sophisticated mathematical model. This being the case, a higher accuracy is achieved by means of complicating the data processing algorithm rather than data expansion typical of modelling or ready sample measurement.

Matching the eye diagram of the transmitted data with the mask corresponding to the worst case of electrical characteristics and jitter is the criterion for conforming a transceiver module to a particular

transmission standard. In this context the value of the total jitter accumulated over a time interval or transmission of a certain code is considered as a parameter. With this approach jitter depends on the transmitted code sequence and the sampling size. This method allows initial evaluation of path performance.

Within the constraints of this model, BER depends heavily on the mutual signal phase at the input of memory elements of the first stage of receiver deserialization. The required condition for receiving correct data by the receiver is providing the allowed timing between switching of the data signal and the clock signal at the trigger input in the digital part of the receiver, as shown in Fig. 2. The data should arrive at the input not later than the minimum setup time ( $T_{setup}$ ) before the clock signal edge. However the data should be held at the input after

- джиттер цифровой части передатчика  $DJ_{TX\_DIG}$  и приемника  $DJ_{RX\_DIG}$ ;

- джиттер драйвера передатчика  $DJ_{TX\_DR}$ ;

- кодозависимый джиттер данных как следствие межсимвольной интерференции  $DJ_{INT}$ ;

- джиттер усилителя приемника  $DJ_{RX\_AMP}$ ;

- функциональный кодозависимый джиттер ВТСД (система восстановления таковых сигналов из данных, англ. — CDR)  $DJ_{CDR}$ ;

- помехи по шине питания передатчика  $DJ_{TX\_VDD}$  и приемника  $DJ_{RX\_VDD}$ ;

- помехи по подложке передатчика  $DJ_{TX\_SUB}$  и приемника  $DJ_{RX\_SUB}$ ;

- неравномерность паразитных структур на шинах тактовых сигналов  $DJ_{CLK\_LAY}$ .

В процессе как проектирования, так и измерения готовых образцов приемопередатчиков может выполняться передача статических последовательностей произвольной длины. Наличие в таких посылках последовательностей битов, имеющих одинаковый логический уровень, приводит к варьированию битовой частоты с точки зрения работы блока ВТСД. Поскольку ВТСД включает в себя инерционные элементы (с задержками), погрешность подстройки фазы сигнала данных становится зависимой от передаваемой последовательности и составляет до 0,5 протяженности битового интервала.

Во время расчета детерминированного джиттера на практике имеет смысл проводить расчет одновременного влияния нескольких детерминированных компонент, таких как

$$DJ^{RX} = JTF(DJ_{PLL}) + JTF(DJ_{TX\_DG}) + JTF(DJ_{TX\_DR}) + JTF(DJ_{INT}) + JTF(DJ_{RX\_AMP}) + JTF(DJ_{RX\_DG}) + JTF(DJ_{TX\_SUB}) + JTF(DJ_{TX\_VDD}) + JTF(DJ_{CDR}) + JTF(DJ_{RX\_SUB}) + JTF(DJ_{RX\_VDD}) + JTF(DJ_{CLK\_LAY}), \quad (4)$$

где  $JTF$  (Jitter Transfer Function) — функция подстройки под джиттер входного сигнала блоком ВТСД приемника.

the clock signal edge for as long as the minimum hold time ( $Thold$ ). If any of the conditions is not met, the writing of correct information is considered to be impossible.

In the presence of phase noise, the receive error probability increases if either the data arrive too late relative to clock signal switch, or the data are held at the input for not long enough.

The probability density of the edges of the investigated signals is described as normal distribution. Error occurrence can be regarded as simultaneous occurrence of two accidental events when the condition of timing between the arrival of the clock signal and the data signal is not met. Figure 3 demonstrates the distribution of the probability density of an event when the minimum  $TSetup$  condition is not met.

The method relies on the principle of building and using a statistical probability

model of error occurrence during transmission of a single bit. At first the transmission path organization is analysed and the jitter of separate blocks in the signal path is calculated. It has been proposed to consider the resulting jitter as normalized to the clock signal jitter relative to the data stream received at the input of memory elements of the first stage of receiver deserialization. Next, the probability density of non-compliance with the requirements of minimum setup and hold time during the writing is calculated (1):

$$DPC = \frac{1}{\sigma\sqrt{2\pi}} e^{\frac{(x-m)^2}{2\sigma^2}}, \quad (1)$$

where  $\sigma$  is the root mean square deviation of the distribution of the clock signal transition moment in the bit interval,  $x$  is the current value of the clock signal transition moment,  $m$  — the mathematical expectation of the transition moment.

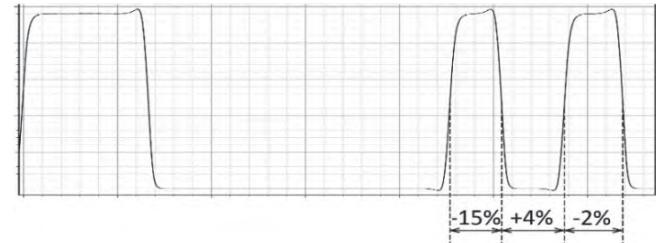

Рис. 5. Влияние межсимвольной интерференции на длительность битового интервала

Fig. 5. The influence of the intersymbol interference on the bit interval length

Приведенный ко входу триггеров приемника битовый интервал равен

$$UI' = UI - DJ^{RX} - Tsetup_{min} - Thold_{min}. \quad (5)$$

В процессе разработки приемопередатчиков транслируемый поток данных принимается псевдослучайным в рамках конкретной кодировки. Как показано ранее, составляющей детерминированного джиттера выступает межсимвольная интерференция, уровень которой зависит от передаваемого кода. Возникающая предыстория длиной в несколько битов приводит к вариации длительности отдельного битового интервала (рис. 5).

Данная модель учитывает различие в длинах битовых интервалов, зависящих от последовательности передаваемых данных. Алгоритм анализирует передаваемый код, составляя битовые шаблоны, учитывающие предысторию длиной в несколько битов данных. Например, если длина шаблона равна 5, общее число шаблонов будет равно 32. В этом случае характеристики последнего бита зависят от последовательности предшествующих четырех битов. Принимая поток данных бесконечным, алгоритм рассчитывает вероятность появления того или иного шаблона, придавая им весовой коэффициент  $P_i$ :

The final step of BER calculation consists in integrating the distribution calculated on the intervals corresponding to bit error occurrence (2):

$$BER = 1 - \int_0^{UI} DPC(t) dt, \quad (2)$$

where  $UI$  is the bit interval of the data signal.

This approach allows calculating bit error ratio within a relatively short time. Nevertheless the accuracy of the obtained result depends to a great extent on the correspondence of the model to the device being developed. Next section describes the aspects significantly improving the accuracy of the calculation.

## THE METHOD OF BER EVALUATION

The elements of the data transmission path may generate both random and deterministic

$$P_i = \frac{D}{N} \cdot M_i, \quad (6)$$

где  $D$  — длина шаблона в битах,  $N$  — общее число переданных битов,  $M_i$  — число повторов  $i$ -го шаблона в выборке из переданных битов.

При этом функция плотности вероятности для каждого из случаев будет иметь вид

$$DPC_i = \frac{1}{\sigma\sqrt{2\pi}} e^{-\frac{(x-m_i)^2}{2\sigma^2}}, \quad (7)$$

где  $m_i$  — математическое ожидание для каждого из вариантов распределения.

Наличие двух и более максимумов распределения момента прихода бита данных означает, что в формуле (4) будут свои слагаемые  $JTF_i(DJ_{INT})$ , а формуле (3) будут использованы свои пределы интегрирования в соответствии с каждым из максимумов распределения сигнала данных. При этом СКО фазы для каждого из распределений принимается одним и тем же. Формула (3) преобразуется в формулу (8) для каждого из шаблонов:

$$BER_i = 1 - \int_{(DJ_{RX}/2) + T_{setup_{min}}}^{UI - (DJ_{RX}/2) - Thold_{min}} DPC_i(t) dt, \quad (8)$$

где  $DJ_i^{RX}$  — результирующий детерминированный джиттер на входе триггера приемника для каждого из случаев.

Таким образом, BER по фазе сигналов будет являться алгебраической суммой BER для каждого из шаблонов с учетом их весовых коэффициентов:

$$BER = \sum_{j=1}^n (P_j \cdot BER_j), \quad (9)$$

где  $n = 2^D$  количество исследованных максимумов распределения.

jitter. Random jitter (RJ) is similar to noise, which makes it possible to define it using the gauss distribution of the signal transition moment. In this case the mathematical expectation and the root mean square deviation will be the parameters. The RJ of the clock signals and the data signals are normalized to the clock signal jitter relative to the data bit interval. Deterministic jitter (DJ) is bounded from above by a maximum value. High frequency DJ results in bit interval reduction. Figure 4 shows bit interval reduction in the presence of high frequency deterministic jitter.

Consequently, when the probability density is integrated in formula (2), it transforms into formula (3):

$$BER = 1 - \int_{(DJ/2) + T_{setup_{min}}}^{UI - (DJ/2) - Thold_{min}} DPC(t) dt. \quad (3)$$

The components of the deterministic jitter are:

- the functional jitter of the phase-locked loop of the transmitter  $DJ_{PLL}$ ;

- the jitter of the digital part of the transmitter  $DJ_{TX\_DIG}$  and the receiver  $DJ_{RX\_DIG}$ ;

Одним из основных источников случайного джиттера системы является ФАПЧ передатчика. Степень подавления фазового шума внешнего опорного сигнала зависит от параметров фильтра и блоков контура умножителя частоты. Джиттер выходного сигнала данных передатчика включает в себя случайный джиттер ФАПЧ, состоящий из собственного шума блоков и той составляющей фазового шума опорного сигнала, которая не была подавлена системой ФАПЧ.

Система восстановления тактового сигнала из данных производит подстройку фазы тактового сигнала передатчика под фазу сигнала данных. Таким образом, происходит подавление случайного джиттера данных, приведенного ко входу триггеров приемника. Степень подавления зависит от параметров блока ВТСД.

Предложенная методика включает в себя математическую модель блоков ФАПЧ и ВТСД, что позволяет рассчитать результирующий случайный джиттер, оказывающий влияние на расчетный BER.

Если фаза тактового сигнала относительно фазы принимаемых данных выходит из области допустимых значений, возникает ошибка записи. Однако в случае записи последовательности битов, имеющих одинаковый логический уровень, данные будут записаны верно, что делает результат оценки BER зависимым от передаваемого кода.

Если величина джиттера тактового сигнала не превышает длительности приведенного ко входу триггеров приемника битового интервала, то ошибка записи может произойти при изменении логического уровня сигнала данных на одной из границ бита. Следовательно, целесообразно рассматривать, помимо BER, частоту ошибок при передаче логических перепадов сигнала данных. Усредненная частота перепадов логического уровня потока данных имеет вид

- the jitter of the transmitter driver  $DJ_{TX\_DR}$ ;

- the code-dependent data jitter as a result of intersymbol interference  $DJ_{INT}$ ;

- the jitter of the receiver amplifier  $DJ_{RX\_AMP}$ ;

- the functional code-dependent CDR jitter  $DJ_{CDR}$ ;

- the noise on the power rails of the transmitter  $DJ_{TX\_VDD}$  and the receiver  $DJ_{RX\_VDD}$ ;

- noise on the substrate of the transmitter  $DJ_{TX\_SUB}$  and the receiver  $DJ_{RX\_SUB}$ ;

- the irregularity of parasitic structures on the clock signal rails  $DJ_{CLK\_LAY}$ .

The processes of designing and measuring ready transceiver prototypes may both include transmission of static test sequences of arbitrary length. The presence of bits with the same logical level in these sequences leads to varying bit frequency in relation to CDR block operation. As far as the CDR block includes delay elements, the data signal phase adjustment inaccuracy becomes dependent on the transmitter sequence and may account for up to 0.5 of the bit interval length.

During the real-world calculation stage it is reasonable to calculate the simultaneous

influence of several deterministic components, such as:

$$\begin{aligned} DJ^{RX} = & JTF(DJ_{PLL}) + JTF(DJ_{TX\_DG}) + \\ & + JTF(DJ_{TX\_DR}) + JTF(DJ_{INT}) + \\ & + JTF(DJ_{RX\_AMP}) + JTF(DJ_{RX\_DG}) + \\ & + JTF(DJ_{TX\_SUB}) + JTF(DJ_{TX\_VDD}) + \\ & + JTF(DJ_{CDR}) + JTF(DJ_{RX\_SUB}) + \\ & + JTF(DJ_{RX\_VDD}) + JTF(DJ_{CLK\_LAY}), \end{aligned} \quad (4)$$

where  $JTF$  is the Jitter Transfer Function.

The bit interval normalized to the receiver trigger input is equal to:

$$UI' = UI - DJ^{RX} - T_{setup_{min}} - Thold_{min}. \quad (5)$$

In the process of transceiver designing the transmitted data stream is considered as pseudorandom within the limits of a particular encoding. As can be seen above, one of the components of the deterministic jitter is the intersymbol interference, whose level depends on the transmitted code. The emerging prehistory of several bits long causes a variation of a single bit interval in length (Fig. 5).

$$f_t = (N_1 + N_2 + N_3 + N_4 + N_5) \cdot \frac{f_b}{M}, \quad (10)$$

где  $f_t$  — частота перепадов логического уровня сигнала данных для 8b/10b кода,  $N_i$  — число последовательностей одинаковых битов длиной  $i$ ,  $M$  — общее число битов в переданной посылке,  $f_b$  — битовая частота передачи.

Данный подход позволяет получить более точное значение частоты битовых ошибок в процессе передачи произвольной посылки данных при известном алгоритме кодировки. Например, поток данных, закодированный по алгоритму 8b/10b, имеет усредненную частоту перепадов, в два раза меньшую битовой частоты. При проведении оценки BER предлагаются делать поправку на соотношение битовой частоты и усредненной частоты передаваемых перепадов логического уровня сигнала данных.

Таким образом, предлагаемая методика оценки частоты возникновения битовых ошибок сводится к следующим шагам:

- выбор кодовых последовательностей, для которых будет проводиться расчет. Наряду со стандартными шаблонами битов, передача которых предполагается при нормальной работе устройства, целесообразно в программу расчета включить наихудшие последовательности, вызывающие джиттер наибольшей величины;

- анализ весовых коэффициентов ( $P_j$ ) шаблонов битов внутри последовательностей и расчет усредненной частоты изменения логического уровня потока данных;

- расчет детерминированного джиттера цифрового тракта, линии передачи и функционального джиттера ВТСД для каждого шаблона битов;

- расчет случайного джиттера ФАПЧ;

This model takes into account the difference in bit interval lengths which depend on the transmitted data. The algorithm analyses the transmitted code and compiles bit patterns including the pre-history of several bits in length. For example, if the pattern length is 5, the total number of patterns will equal 32. In this case the characteristics of the last bit depend on the sequence of the preceding four bits. Taking the data stream as infinite, the algorithm calculates the probability of a pattern by adding a weighting factor of  $P_j$ :

$$P_j = \frac{D}{N} \cdot M_j, \quad (6)$$

where  $D$  is the bit length of a pattern,  $N$  — the total number of the transmitted bits,  $M_j$  — the repeat count of the  $j^{\text{th}}$  pattern in the sampling of the transmitted bits.

The function of probability density for each of the cases will have the following form:

$$DPC_j = \frac{1}{\sigma \sqrt{2\pi}} e^{-\frac{(x-m_j)^2}{2\sigma^2}}, \quad (7)$$

where  $m_j$  is the mathematical expectation for each of the distribution options.

The existence of two or more maxima of distribution of the data bit arrival moment means that formula (4) will have different addends  $JTF_j(DJ_{j,\text{INT}})$  and formula (3) will have different limits of integration in accordance with each of the maxima of the data signal distribution. In this case the root mean square deviation of the phase for each of the distributions is considered the same. Formula (3) transforms into formula (8) for each of the patterns:

$$BER_j = 1 - \int_{(DJ_{j,\text{RX}}/2) + T_{\text{setup},\min}}^{UI - (DJ_{j,\text{RX}}/2) - T_{\text{hold},\min}} DPC_j(t) dt, \quad (8)$$

where  $DJ_{j,\text{RX}}$  is the resulting deterministic jitter at the receiver trigger input for each of the options.

Therefore, BER of the signal phase will be the algebraic sum of BER values for each of the patterns with account of their weighting factors:

$$BER = \sum_{j=1}^n (P_j \cdot BER_j), \quad (9)$$

where  $n = 2^D$  is the number of investigated distribution maxima.

PLL of the transmitter is one of the main sources of random jitter of the system. The degree of phase noise suppression of the external reference signal depends on the parameters of the filter and the frequency multiplier circuit blocks. The data output signal jitter of the transmitter includes the random PLL jitter consisting of the internal block noise and the component of the reference signal noise which was not suppressed by the phased-locked loop system.

The system of clock and data recovery adjusts the transmitter clock signal phase to the data signal phase. This way the random data jitter normalized to the receiver trigger input is suppressed. The degree of suppression depends on CDR block parameters.

The proposed method includes the mathematical model of the PLL and CDR blocks, which allows calculating the resulting random jitter influencing the calculated BER.

If the clock signal phase relative to the received data phase is beyond the tolerance

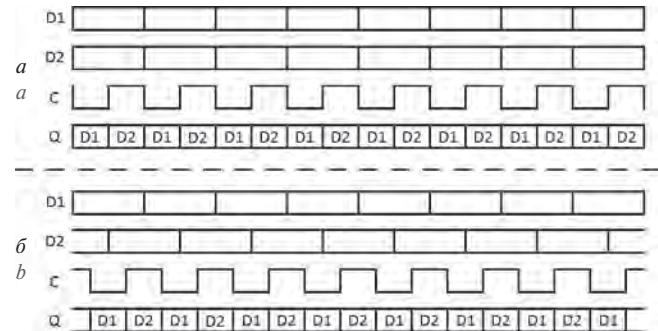

Рис. 6. Варианты взаимной фазы сигналов на входе оконечного мультиплексора передатчика

Fig. 6. Variations of the mutual signal phase at the input of the terminating transmitter multiplexer

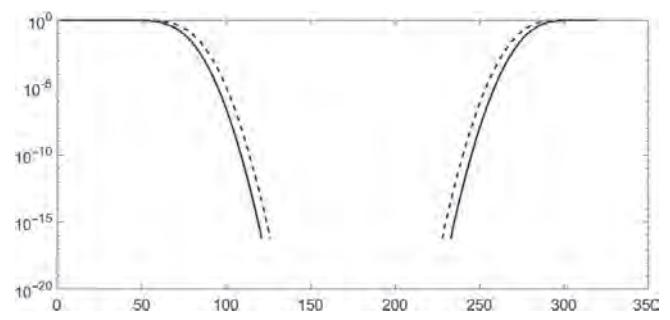

Рис. 7. BER диаграммы для случая А (прерывистая) и случая Б (сплошная)

Fig. 7. BER graphs for cases A (dashed) and B (solid)

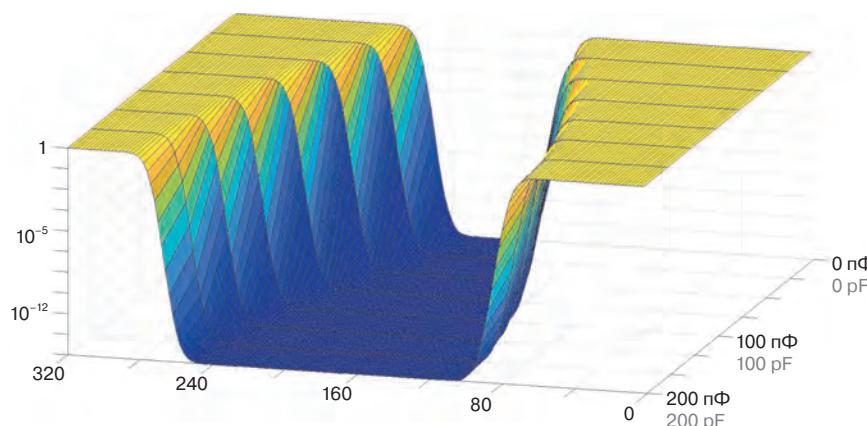

Рис. 8. Трехмерная BER-диаграмма зависимости запаса по фазе подстройки приемника от номинала демпфирующего конденсатора стабилизаторов питания

Fig. 8. A 3D BER graph demonstrating the relation of the phase margin of the receiver adjustment relative to the incoming data phase to the nominal value of the damping capacitor of the supply stabilizer

- расчет случайного джиттера выходного тактового сигнала ВТСД относительно фазы потока данных;

- приведение компонент джиттера ко входу элементов памяти первой ступени десериализации приемника;

- интегрирование распределения плотности вероятностей с поправкой на частоту изменения логического уровня потока данных;

- получение результирующего BER для каждой кодовой последовательности битов;

- построение BER-диаграммы — зависимости частоты ошибок от положения тактового сигнала памяти приемника относительно принимаемого битового интервала.

### ПРИМЕНЕНИЕ МЕТОДИКИ

Разработанная методика была использована при проектировании мультискоростного приемопередатчика последовательного канала стандарта SpaceFibre, работающего на частотах от 5 Мбит/с до 3,125 Гбит/с, в целях уменьшения BER. Результаты оценки BER позволили произвести серию улучшений конструкции приемопередатчика. Некоторые из них описаны далее.

В целях обеспечения передачи битов в широком диапазоне скоростей разработан блок синхронизации дерева тактовых сигналов, также цифровая часть разделена на два параллельных конвейера данных для работы в НЧ-области (5–125 Мбит/с) и ВЧ-области (1,25–2,5 Гбит/с). Передача на частоте 3,125 Гбит/с достигается путем увеличения частоты опорного сигнала ФАПЧ.

Цифровая часть выполняет функцию свертки групп параллельных битов в последовательный поток. В рамках данной работы принимается, что функциональные ошибки, а также ошибки, связанные с нарушением требований по быстродействию в блоках синхронизации дерева тактовых сигналов, а также в блоках групповых операций, отсутствуют. Тем самым, внимание уделено цепям битовых операций как работающим на частотах, сопоставимых с битовыми частотами передачи, а также блокам ФАПЧ и ВТСД. Далее представлены примеры использования разработанной методики.

range, a writing error occurs. However, if a sequence of bits with the same logical level is written correctly, the BER evaluation result will depend on the transmitted code.

If the value of the clock signal jitter does not exceed the length of the bit interval normalized to the receiver trigger input, a writing error may occur upon changing the logical level of the data signal at one of the bit boundaries. Therefore, there is a good reason to consider, besides BER, the error rate occurring at transmitting logic transitions of the data signal. The average rate of logical level transitions of the data stream is written as:

$$f_t = (N_1 + N_2 + N_3 + N_4 + N_5) \cdot \frac{f_b}{M}, \quad (10)$$

where  $f_t$  is the transition rate of the data signal logical level for 8b/10b code,  $N_i$  — the number of sequences of the same bits of  $i$  length,  $M$  — the total number of bits in the transmitted pattern,  $f_b$  — the transmission bit rate.

This approach allows obtaining a more accurate value of the rate of the bit errors occurring in the process of transmission

of an arbitrary data pattern using a certain coding algorithm. For example, the average transition rate of the data stream encoded by 8b/10b algorithm is half as large as the bit rate. It is proposed to make a correction for the ratio of the bit rate and the average rate of the transmitted logical level transitions of the data signal in the process of BER evaluation.

Summarizing the above, the proposed method of bit error rate evaluation resolves into the following steps:

- selection of code sequences for which the calculation will be performed. It is advisable to include the worst patterns causing the largest jitter in the calculation along with the standard bit patterns to be transmitted under normal device operation;

- analysis of the weighting factors ( $P_i$ ) of the bit patterns in the sequences and calculation of the average rate of the logical level transition of the data stream;

- calculation of the deterministic jitter of the digital path, transmission line and the functional CDR jitter for each of the bit patterns;

- calculation of the random PLL jitter;

- calculation of the random jitter of the output clock CDR signal relative to the data stream phase;

- normalizing the jitter components to the input of memory elements of the first stage of receiver deserialization;

- integrating the probability density with the adjustment for the rate of the logic transition level of the data stream;

- obtaining the resulting BER for each code bit sequence;

- construction of a BER diagram — the variation of the error rate with respect to the position of the clock signal of the receiver memory relative to the received bit interval.

### APPLICATION OF THE METHOD

The developed method was used to reduce BER in the process of designing a SpaceFibre compliant multispeed serial channel transceiver operating in the 5 Mbit/s—3.125 Gbit/s frequency range. The BER evaluation results allowed a series of improvements in the transceiver design. Some of them are described below:

Основным источником  $DJ_{TX\_DG}$  передаваемых данных является выходной мультиплексор 2 в 1, преобразующий два параллельных потока данных в последовательный. В процессе сериализации происходит пропорциональное умножение частоты сигнала, что увеличивает отношение детерминированного джиттера к длительности битового интервала. Вариации технологического процесса, а также изменение температуры приборов приводят к дрейфу сигналов адреса С на входе мультиплексора по отношению к сигналам мультилиплицируемых данных D1 и D2. Разработанная методика была применена в целях определения зависимости BER от типа взаимной фазы сигналов на входе мультиплексора. Рассмотрены два типа формирования таких сигналов: со взаимным смещением сигналов данных (рис. 6а) и без смещения (рис. 6б).

На рис. 7 представлены BER-диаграммы для случаев А и Б. Использование схемы, соответствующей случаю Б (сплошная кривая на графике), позволяет увеличить запас позиционирования тактового сигнала внутри битового интервала на 10 %. Формирование смещенных данных требует использования нескольких фаз высокочастотных тактовых сигналов, что увеличивает сложность устройства передатчика. Однако данное решение является целесообразным, поскольку оно позволяет достичь значительного прироста запаса по фазе.

Синхронное переключение элементов цифрового домена приемопередатчика, а также наличие паразитных индуктивностей корпуса приводят к появлению пульсаций (170 мВ) по шинам питания и земли. Это приводит к возникновению дополнительной детерминированной фазовой ошибки в тракте следования данных, а также к увеличению джиттера блоков ФАПЧ и ВТСД. В целях уменьшения взаимного влияния блоков

друг на друга общие шины питания приемника и передатчика были разделены на отдельные области для цифровых и аналоговых доменов. Каждый домен питается от понижающих стабилизаторов напряжения с 2,5 до 1,2 В. Это позволило снизить пульсации шины питания до 30 мВ. На рис. 8 изображена трехмерная BER-диаграмма, описывающая параметрическую зависимость частоты ошибок от демпфирующей емкости стабилизаторов напряжения передатчика.

В соответствии с полученной зависимостью был выбран номинал конденсатора, равный 100 пФ, как компромиссный с точки зрения величины джиттера данных и занимаемой площади.

Модификации устройства передатчика и приемника привели к уменьшению джиттера тактовых сигналов и передаваемых данных, что, согласно BER-диаграммам, позволило увеличить фазовый запас подстройки тактового сигнала приемника под принимаемые данные на 20 %.

## ЗАКЛЮЧЕНИЕ

Проведена разработка универсальной методики оценки частоты возникновения битовых ошибок (BER) в приемопередатчиках последовательного канала на этапе проектирования.

Данная методика использована в процессе разработки мультикоростного приемопередатчика стандарта SpaceFibre, работающего на частотах от 5 Мбит/с до 3,125 Гбит/с. Произведена оптимизация по критерию минимального джиттера каждого из критических блоков устройства, что позволяет увеличить фазовый запас подстройки тактового сигнала приемника относительно фазы принимаемых данных на 45 %.

Авторы считают, что в данной работе новыми являются следующие положения:

To provide bit transmission in a wide speed range, a clock signal tree synchronization block has been developed. The digital part has been divided into two parallel data pipes to provide operation in the low-frequency (5–250 Mbit/s) and the high frequency (1.25–2.5 Gbit/s) ranges. Transmission at the frequency of 3.125 Gbit/s is provided by means of increasing the frequency of PLL reference signal.

The function of the digital part is to convert groups of parallel bits into a sequential stream. This paper assumes that there are no functional errors as well as errors connected with the non-compliance with the speed performance requirements on clock signal tree synchronization blocks and group operation blocks. The paper focuses on bit operation chains as operating at the frequencies comparable to transmission bit frequencies as well as on PLL and CDR blocks. Below you will find examples of the developed method application.

The output 2-in-1 multiplexer converting two parallel streams into a serial one is the main source  $DJ_{TX\_DG}$  of the transmitted data.

The signal frequency is multiplied proportionally during the serialization, which increases the ratio of the deterministic jitter to the bit interval length. Variations of the technology process and the device temperature result in C address signal drift at the multiplexer input relative to D1 and D2 signals of the data being multiplied. The developed method was used to determine the dependence of BER on the type of the mutual signal phase at the multiplexer input. Two types of such signals have been considered: with a data signal shift (Fig. 6 A) and without it (Fig. 6 B).

Figure 7 presents BER graphs for A and B cases. The scheme corresponding to B case (the solid line on the graph) allows increasing the positioning margin of the clock signal within the bit interval by 10 %. Forming shifted data requires several phases of high-frequency clock signals, which complicates the transmitter design. Nevertheless, this solution is feasible because it provides a significant phase margin increment.

Synchronous switching of elements of the transceiver block digital domain as well as parasitic inductances of the package

cause pulsations (170 mV) on the power and grounding rails. This induces an additional deterministic phase error in the data path and higher PLL and CDR jitters. To reduce the mutual influence of the blocks, the common power rails of the transmitter and the receiver should be split into separate areas for the digital and the analogous domains. Each domain is supplied with 2.5 to 1.2 V voltage step-down stabilizers. This reduced the supply rail pulsations to 30 mV. Figure 8 shows a 3D BER graph which describes the parametric dependence of the error rate on the damping capacity of the transmitter voltage stabilizers.

According to the obtained relation, the nominal value of the capacitor has been chosen to be 100 pF, which is a trade-off between the data jitter and the occupied area.

Modifications in the design of the transmitter and the receiver allowed reduction in the clock signal jitter and the transmitted data jitter, which, according to BER graphs, increased the phase margin of the receiver clock signal adjustment in accordance with the received data by 20 %.

- комплексный статистический анализ зависимости BER от работы структурных элементов приемопередатчика;

- обработка уникальных шаблонов битов в составе передаваемой псевдослучайной кодовой последовательности с их весовыми коэффициентами;

- оценка вероятности возникновения битовой ошибки при изменении логического уровня передаваемого сигнала данных.

Учет ключевых факторов, влияющих на джиттер тракта трансляции данных, а также их вариативность внутри модели облегчают проведение системного анализа работы структурных элементов приемопередатчика в целях поиска блоков, вносящих наибольший вклад в увеличение BER с последующей их оптимизацией.

#### ЛИТЕРАТУРА

1. Parkes S., Ferrer A., Gonzalez A. and McClements C. *SpaceFibre Specification Draft H9*. University of Dundee, 2017. 233 p.

#### CONCLUSIONS

A universal method of evaluating the bit error rate (BER) in serial channel transceivers at the design stage has been developed.

This method was applied in the process of developing a SpaceFibre compliant multispeed transceiver operating at frequencies of 5 Mbit/s—3.125 Gbit/s. Each of the critical blocks of the device was optimized with respect to the minimum jitter requirement, which resulted in increasing the phase margin of the receiver clock signal adjustment in accordance with the received data phase by 45%.

The authors consider the following results as novel:

- comprehensive statistical analysis of BER dependence on the functioning of the transceiver structural elements;

- processing unique bit patterns within the transmitted pseudorandom code sequence with their weighting factors;

- estimating probability of a bit error occurring on changing the logical level of the transmitted data signal.

Taking account of the key factors influencing the data transmission path jitter as well as their variability within the model simplifies the system analysis of the transceiver structural elements functioning in order to find the blocks that contribute most to increasing BER with their further optimization.

#### REFERENCES

1. Parkes S., Ferrer A., Gonzalez A. and McClements C. *SpaceFibre Specification Draft H9*. University of Dundee, 2017. 233 p.

2. Mitić D., Lebl A., Markov Ž. *Calculating the Required Number of Bits in the Function of Confidence Level and Error Probability Estimation* // Serbian journal of electrical engineering. Vol. 9. № 3. 2012. P. 361–375.

3. Duan Y., Chen D. *Fast and Accurate Decomposition of Deterministic Jitter Components in High-Speed Links* // IEEE Transactions on Electromagnetic Compatibility. Vol. 9. № 99. 2018. P. 1–9.

4. Bidaj K., Begueret J., Houdali N. *Time-domain PLL modeling and RJ / DJ jitter decomposition* // IEEE International Symposium on Circuits and Systems (ISCAS), 2016. P. 185–188.

5. Liang J., Sheikholeslami A., Tamura H., Yamaguchi H. *On-Chip Jitter Measurement Using Jitter Injection in a 28 Gb/s PI-Based CDR* // IEEE Journal of Solid-State Circuits. Vol. 53. № 3. 2018. P. 750–761.

6. Доможаков Д.А., Дубинский А.В., Раннев Н.Ю. Методика расчета вероятности возникновения ошибок в высокоскоростных каналах связи // Проблемы разработки микроприборов и наноэлектронных систем, ч. 2, 2016. — С. 164–168.

3. Duan Y., Chen D. *Fast and Accurate Decomposition of Deterministic Jitter Components in High-Speed Links* // IEEE Transactions on Electromagnetic Compatibility. Vol. 9. № 99. 2018. P. 1–9.

4. Bidaj K., Begueret J., Houdali N. *Time-domain PLL modeling and RJ / DJ jitter decomposition* // IEEE International Symposium on Circuits and Systems (ISCAS), 2016. P. 185–188.

5. Liang J., Sheikholeslami A., Tamura H., Yamaguchi H. *On-Chip Jitter Measurement Using Jitter Injection in a 28 Gb/s PI-Based CDR* // IEEE Journal of Solid-State Circuits. Vol. 53. № 3. 2018. P. 750–761.

6. Domozhakov D.A., Dubinskii A.V., Rannnev N.Yu. Metodika rascheta veroyatnosti vozniknoveniya oshibok v vysokoskorostnykh kanalakh svyazi // Problemy razrabotki mikro- i nanoelektronnykh sistem, ch. 2, 2016. P. 164–168. (In Russian).

**ТЕХНОСФЕРА**

РЕКЛАМНО-ИЗДАТЕЛЬСКИЙ ЦЕНТР

[www.technosphera.ru](http://www.technosphera.ru)

ЭЛЕКТРОНИКА | НАНОИНДУСТРИЯ | ФОТОНИКА | ПЕРВАЯ МИЛЯ | Аналитика | СТАНДАРТИНСТРУМЕНТ

Издательский дом | Наноиндустрия | Фотоника | Первая Милия | Аналитика | Стандартизация | Проектирование | Производство