УДК 621.382, ББК 32.853.1

DOI: 10.22184/NanoRus.2019.12.89.297.298

# ИНТЕГРИРОВАННОЕ РЕШЕНИЕ ПАРИРОВАНИЯ ТИРИСТОРНОГО ЭФФЕКТА ДЛЯ СБИС СнК

## INTEGRATED SOLUTION FOR PARRYING THYRISTOR EFFECT FOR VLSI SOC

МАТВЕЕВ ДМИТРИЙ ВАЛЕРЬЕВИЧ

d.matveev@mri-progress.ru

MATVEEV DMITRIY V.

d.matveev@mri-progress.ru

ГАЛИМОВ АРТУР МАРАТОВИЧ

ФАТЕЕВ ИВАН АЛЕКСАНДРОВИЧ

КУЛИКОВ ДМИТРИЙ ВАСИЛЬЕВИЧ

GALIMOV ARTUR M.

FATEEV IVAN A.

KULIKOV DMITRIY V.

АО «НИИМА «Прогресс»

125183, г. Москва, проезд Черепановых, 54Microelectronics Research Institute PROGRESS JSC

("PROGRESS MRI" JSC)

54 Cherepanovych Lane, Moscow, 125183, Russia

В работе рассматриваются аппаратные способы парирования тиристорного эффекта. Для исследования характеристик и способов обнаружения тиристорного эффекта разработаны тестовые схемы.

**Ключевые слова:** одиночный тиристорный эффект; схема парирования тиристорного эффекта.

The paper considers hardware SEL parry techniques. Test circuits have been developed to obtain characteristics of parasitic latch and to study methods of detecting thyristor effect.

**Keywords:** single event latch-up; latch-up recovery circuit.

### ВВЕДЕНИЕ

Одной из актуальных проблем при проектировании стойких к радиационным эффектам СБИС является задача снижения чувствительности интегральных схем к тиристорному эффекту (ТЭ). Целью настоящей работы является модернизация способов повышения живучести микросхем в условиях появления ТЭ.

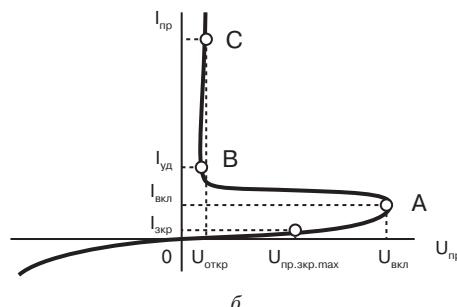

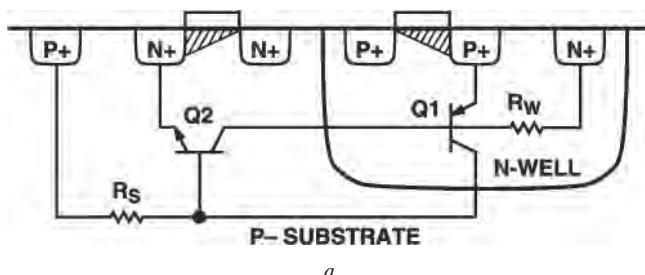

При попадании тяжелых заряженных частиц (ТЗЧ) в чувствительную область микросхемы в подложке возникает индуцированный импульс тока. Сопротивление подложки  $R_S$  (рис. 1a) создает положительное смещение между областями базы и эмиттера паразитного биполярного транзистора  $Q2$ , что может привести к включению тиристорной структуры. Вольт-амперная характеристика этой структуры имеет нелинейность — участок отрицательного дифференциального сопротивления АВ (рис. 1б) с последующим резким ростом тока ВС (рис. 1б). Таким образом, между контактами питания формируется состояние короткого замыкания. В зависимости от расположения и параметров структур, технологических размеров ток короткого замыкания варьируется от сотен мкА до сотен мА. Этот эффект может иметь деструктивный характер последствий для микросхем — «выгорание» элементов, т. е. катастрофический отказ.

Максимального снижения чувствительности микросхем к ТЭ можно добиться использованием кольцевых контактов вокруг каждого транзистора в целях минимизации сопротивления базы паразитного биполярного транзистора [1]. К сожалению, не во всех технологиях доступны готовые библиотеки стандартных элементов с дополнительными контактами к подложке и карману и инструменты, позволяющие избежать образования паразитных биполярных транзисторов.

### ПРЕДЛАГАЕМЫЙ СПОСОБ ЗАЩИТЫ ИС ОТ ПОСЛЕДСТВИЙ ТЭ

Аппаратный способ обнаружения и подавления ТЭ является более универсальным и позволяет системе на кристалле (СнК) без внешнего вмешательства избежать длительного разрушительного воздействия. Активные схемы защиты обнаруживают аномальный рост тока потребления, характерный для включения тиристора. После этого принимается решение об ограничении протекающего тока до значений токов удержания тиристора и ниже или произведения сброса системы питания.

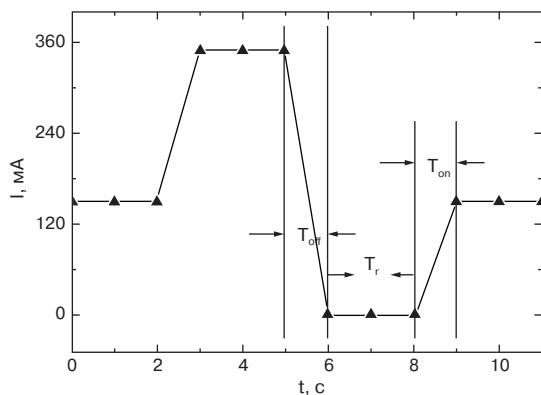

На рис. 2 представлена последовательность срабатывания механизма защиты. После обнаружения повышенного тока

Рис. 1. а) Сечение КМОП-инвертора с паразитной тиристорной структурой; б) вольт-амперная характеристика тиристора

Рис. 2. Последовательность работы схемы защиты от ТЭ

время выключения/включения ( $T_{off}/T_{on}$ ) определяется суммарной емкостью, а необходимое время восстановления ( $T_r$ ) задается разработчиком.

Понижение напряжения питания цифровых схем, введение ретроградного профиля распределения примеси и другие мероприятия по ухудшению параметров паразитных биполярных транзисторов, безусловно, улучшили надежность микросхем в части борьбы с ТЭ [1]. Вместе с этим уменьшились значения токов тиристора. Поэтому для современных полупроводниковых технологий обнаружение тока тиристора на фоне рабочего тока потребления является трудоемкой задачей. В условиях динамического управления ресурсами СнК так называемые микрозашелки могут оставаться незамеченными во время работы устройства или вызывать функциональные сбои узлов пораженной схемы и привести впоследствии к выгоранию элементов СБИС СнК.

В рамках данной работы предложена идея сложно-функционального блока для защиты интегральной схемы от ТЭ. Его функции заключаются в своевременном обнаружении повышения потребляемого тока и обеспечении последовательности действий по сбросу питания и восстановлению работы блока или СнК. Существующие решения с применением внешних по отношению к защищаемому объекту микросхем активного парирования ТЭ имеют существенные ограничения (микросхемы НПК ТЦ 1469ТК035, 1469ТК035). Например, для некоторых интегральных схем время парирования превышает допустимое время нахождения этих схем в состоянии ТЭ. Учитывая механизм распространения тиристорного эффекта, называемого в литературе эффектом домино [2], включающий постепенно все большее количество тиристоров, временной промежуток от возникновения первичного тиристора до момента обнаружения схемой защиты можно считать достаточным для появления скрытых дефектов из-за нагрева.

Также необходимо учитывать, что максимальный ток потребления СнК не может являться пороговым для активной схемы парирования, т. к. в системах с динамическим управлением питания ток потребления находится в зависимости от конфигурации самой системы. Из-за возможности перехода некоторых элементов в режим пониженного энергопотребления диапазон значений тока потребления СнК значительно больше значений токов в состоянии ТЭ. Поэтому одним из требований к разрабатываемому блоку является адаптивность средств контроля потребляемого тока к состоянию защищаемого объекта и, следовательно, возможность задания динамического порога срабатывания.

Схема защиты от тиристорного эффекта содержит детектор тока и компаратор как основные компоненты [3, 4]. Чаще всего ток преобразуется в напряжение и сравниваются аналоговые или цифровые значения. При использовании цифрового управления

большой точности сравнения можно добиться, измеряя напряжение с помощью аналого-цифровых преобразователей (АЦП). Однако проектирование радиационно-стойкого АЦП является нетривиальной задачей. Поэтому в большинстве схем [3, 4] реализовано аналоговое управление ключами питания от компаратора напряжения, отслеживающего падение напряжения на шунтирующем резисторе. Задание порогового тока осуществляется использованием резистора с необходимым значением сопротивления. Стоит также упомянуть, что существенная зависимость токов от температуры дополнительна усложняет процесс измерений.

Сама схема защиты должна обладать повышенной стойкостью к радиационным эффектам. Например, влияние дозовых эффектов обычно характеризуется постепенным увеличением рабочего тока, что в определенный момент может привести к постоянному выходу схемы в состояние сброса питания. Поэтому проектирование топологии данной схемы предусматривает рациональное использование стандартных методов обеспечения радиационной стойкости ввиду критичности ее функций.

В данной работе выбрана реализация схемы обнаружения ТЭ в виде генератора импульсов с зависимостью частоты от тока заряда конденсатора. С помощью токового зеркала с известным коэффициентом деления ток потребления блока направляется на вход генератора, частота импульсов которого измеряется относительно известной опорной частоты. Таким образом, появляется возможность сравнения цифровых значений тока потребления СБИС во время ее работы со значениями в нормальных условиях. В качестве испытуемых объектов использованы цифровые блоки, которые содержат умножители, обладающие высоким энергопотреблением. Благодаря возможностям отключения синхросигнала набор этих блоков создает систему с широким диапазоном тока потребления. С помощью импульсного лазерного воздействия планируется провести эффективность выработанных методов. В ходе исследования планируется оценить токи удержания тиристоров, точность измерения тока потребления и уровень стойкости схемы защиты.

## ЗАКЛЮЧЕНИЕ

Использование интегрированных в защищаемый объект активных элементов парирования ТЭ позволит максимально эффективно отслеживать состояние микросхемы, а также сократить время срабатывания механизма защиты. Для решения задач интеграции подобных элементов в СБИС авторами проводится исследование пороговых напряжений и токов удержания тиристорных паразитных схем с помощью специальных тестовых структур. Это позволит усовершенствовать существующие методы обнаружения тиристорного эффекта для ускорения механизма защиты и в конечном итоге повысить надежность микросхемы.

## ЛИТЕРАТУРА

1. Boselli G., Reddy V. and Duvvury C. *Latch-up in 65nm CMOS technology: A scaling perspective* // Proceedings of the International Reliability Physics Symposium. Apr. 2005. P. 137–144.

2. Dodds N. A. *Single event latchup: hardening strategies, triggering mechanisms, and testing considerations* // Ph. D. Thesis (Nathaniel: Graduate School of Vanderbilt University), 2012. P. 57–68.

3. Патент 2305894 РФ, Н03К 17/08. Устройство для защиты интегральных микросхем при попадании в них тяжелых частиц / Фильцер И. Г.; ФГУП НИИ точных приборов; № 2005126061/09, заявлено 17.08.2005; опубл. 10.09.2007.

4. Патент 2405247 РФ, Н03К 17/08. Устройство защиты цифровых микросхем / Чирков А. В., Колмаков В. В.; ОАО ИСС; № 2009109340/08, заявлено 13.03.2009; опубл. 27.11.2010.