УДК 621.382

DOI: 10.22184/NanoRus.2019.12.89.321.324

## СИНТЕЗАТОР ВИДЕОКОНТРОЛЛЕРА ПО ТЕХНОЛОГИИ 65 НМ ДЛЯ МОНИТОРОВ С РАЗРЕШЕНИЕМ ДО 4K

## A 65-NM VIDEOCONTROLLER SYNTHESIZER FOR MONITORS WITH RESOLUTION UP TO 4K

АГАФОНОВ АРТЕМ ЕВГЕНЬЕВИЧ AGAFONOV ARTEM E.

БОРОШКО СЕРГЕЙ ИВАНОВИЧ BOROSHKO SERGEY I.

КИРИЧЕНКО ПАВЕЛ ГРИГОРЬЕВИЧ KIRICHENKO PAVEL G.

pgkirich@cs.niisi.ras.ru pgkirich@cs.niisi.ras.ru

СЫСОЕВА ОЛЬГА ВЯЧЕСЛАВОВНА SYSOEVA OLGA V.

ТАРАСОВ ИГОРЬ ВЛАДИМИРОВИЧ TARASOV IGOR V.

XOXЛOBA АННА ГЕННАЛЬЕВНА KHOKHLOVA ANNA G.

ФГУ ФНЦ НИИСИ РАН SRISA RAS

117218, Москва, Нахимовский просп., 36, к. 1 bld. 1, 36 Nakhimovskiy Ave., Moscow, 117218

Рассмотрен процесс разработки синтезатора частот с блоком фазовой автоподстройки частоты (ФАПЧ) со схемой автосмещения и программируемым блоком накачки заряда (БНЗ) для видеоконтроллера. Предложена архитектура синтезатора, позволяющая получить тактовую частоту интерфейса с шагом 250 кГц и менее без применения дельта-сигма-модулятора, фазового интерполятора и рандомизатора в петле обратной связи.

Ключевые слова: ФАПЧ; синтезатор частот; видеоконтроллер.

The paper highlights the design process of clock synthesizer for videocontroller implementation based on phase-locked loop (PLL) with autoshifting circuit and programmable charge pump (CP). An architecture of synthesizer for interface clock frequency with step 250 kHz and less without delta-sigma modulator, phase interpolator and randomizator in the feedback loop has been proposed. *Keywords: PLL; clock synthesizer; videocontroller.*

Основной функцией синтезатора частоты является преобразование входного опорного низкочастотного сигнала в высокочастотный. Из-за разнообразия областей применения синтезаторов возникают требования к достаточной гибкости последних: широком диапазоне входных и выходных частот при сохранении стабильности работы и минимальной величине фазового дрожания (джиттера) выходного сигнала. Так, например, в видеоконтроллерах погрешность установки частоты должна находиться в диапазоне ±0,5%. При этом номинальное значение пиксельной частоты в соответствии со стандартами VESA, как правило, задается с точностью 250 кГц. Для примера пиксельная частота монитора с популярным разрешением 1920×1200 пикселей и кадровой частотой 60 Гц составляет 193,250 МГц. При реализации НДМІинтерфейса пиксельная частота умножается на 7 и составляет 1352,75 МГц. Таким образом, к синтезаторам видеоконтроллеров предъявляются жесткие требования обеспечения установки высокочастотного сигнала в широком диапазоне с точностью до 250 кГц и погрешностью, не превышающей полпроцента. Эти задачи были решены в ходе выполнения работы, описанной в данной статье.

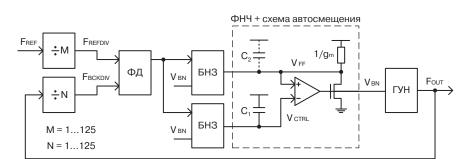

В стандартной архитектуре однопетлевой синтезатор на основе блока фазовой автоподстройки частоты (ФАПЧ) включает в себя перестраиваемый генератор, управляемый напряжением (ГУН), сигнал которого после требуемого (программируемого) деления на N по частоте ( $F_{BCKDIV}$ ) подается на один

из входов фазового детектора. Другой вход фазового детектора подключен к делителю на М опорного сигнала ( $F_{REFDIV}$ ). Фазовый детектор сравнивает сигналы на двух входах и генерирует сигнал ошибки, который поступает на вход блока накачки заряда (БНЗ). Последний, в свою очередь, формирует соответствующий корректирующий импульсный заряд большой амплитуды и малой длительности, который проходит далее через ФНЧ и подстраивает частоту ГУН к нужной выходной частоте. В установившемся состоянии синтезатор генерирует выходную частоту  $F_{OUT}$ , в N/M раз большую, чем опорная частота  $F_{RFF}$ .

Однако в синтезаторе, построенном по этой ставшей классической архитектуре, параметры, определяющие полосу пропускания и коэффициент затухания, являются строго фиксированными, что ограничивает возможные частотные диапазоны сигналов  $\mathbf{F}_{\text{REF}}$  и  $\mathbf{F}_{\text{OUT}}$ .

Синтезатор частоты на основе ФАПЧ со схемой автосмещения [1,2] решает эту проблему: вместо фиксированного сопротивления в фильтре низких частот в рассматриваемом синтезаторе используется сопротивление  $1/g_m$ , пропорциональное периоду выходной частоты, как показано на рис. 1. Также БНЗ может быть сделан программируемым. В этом случае его основу составляет набор переключаемых двоично-взвешенных источников тока, которые управляют величиной корректирующего импульсного заряда.

Рис. 1. Архитектура синтезатора частоты на основе ФАПЧ со схемой автосмещения

При этом, однако, возникает другая проблема, связанная с появлением фазового дрожания выходного сигнала (периодического джиттера). В особенности это заметно при уменьшении напряжения питания и/или при увеличении выходной частоты. Причиной появления джиттера является приход корректирующего сигнала с БНЗ на ГУН, что приводит к резкому изменению частоты последнего [3]. Это повторяется при каждом сравнении  $F_{\text{REFDIV}}$  и  $F_{\text{BCKDIV}}$  сигналов фазовым детектором (рис. 2a).

В рассмотренных выше примерах проблема джиттера частично решается путем добавления шунтирующего конденсатора С,

FREFDIV

FBCKDIV

Добавление C<sub>2</sub>

V CTRL

FOUT

A

V CTRL

FOUT

6

Рис. 2. Периодический джиттер (а) в синтезаторе со стандартной архитектурой (б) в синтезаторе с дискретным  $\Phi$ HЧ

в ФНЧ [2], что сглаживает амплитуду корректирующего сигнала (рис. 2a). Недостатком данного решения является уменьшение устойчивости всей системы при некоторых значениях коэффициента деления выходной частоты N.

Проблему устойчивости синтезатора позволяет решить архитектура с дискретным ФНЧ [3, 4], что позволяет уменьшить амплитуду импульсного сигнала ошибки и расширить его на весь период сигнала  $F_{\text{REFDIV}}$  (рис.  $2\delta$ ).

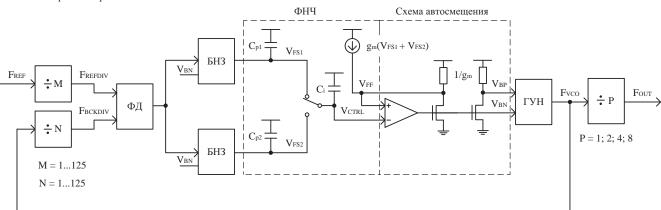

Схема, использующая такую архитектуру, представлена на рис. 3. Здесь ФНЧ реализован на переключаемых конденсаторах. Импульсный сигнал ошибки поступает с БНЗ на емкость  $C_{Pl}$  или  $C_{P2}$ . Пока один из конденсаторов  $C_{Pl}$  или  $C_{P2}$  накапливает заряд, другой,  $C_{P2}$  или  $C_{Pl}$  соответственно, находится в состоянии сброса заряда на интегрирующую емкость  $C_{I}$  (на рис. 4  $C_{P2}$  накапливает заряд,  $C_{Pl}$  находится в состоянии сброса). Сигналы ошибок  $V_{FSl}$  и  $V_{FS2}$  суммируются и подаются на схему автосмещения, которая корректирует сигналы  $V_{BN}$  и  $V_{BP}$ . После ГУН в схему синтезатора частоты для расширения диапазона частот

выходного сигнала  $F_{\text{оит}}$  добавлен дополнительный программируемый делитель выходной частоты на P (коэффициенты деления на 1, 2, 4, 8).

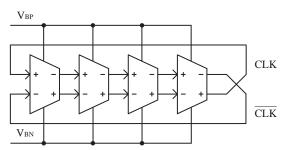

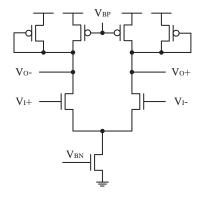

ГУН в данном синтезаторе реализован на основе кольцевого генератора [1, 2], показанного на рис. 4. Его основу составляют дифференциальные буферные каскады задержки с симметричными нагрузками на р-канальных транзисторах и динамической подстройкой смещения  $V_{BN}$  и  $V_{BP}$ , изображенные на рис. 5, что обеспечивает широкий диапазон настройки скорости переключения буферных каскадов и существенное снижение влияния шумов по питанию на выходной джиттер.

Предложенная архитектура синтезатора частоты на основе ФАПЧ обеспечивает широкий диапазон умножения входного опорного низкочастотного сигнала, что позволяет использовать данный

Рис. З. Архитектура синтезатора частоты на основе ФАПЧ со схемой автосмещения и дискретным ФНЧ

синтезатор во многих интегральных схемах. Схема автосмещения гарантирует стабильную работу системы при различных коэффициентах умножения частоты и уменьшает влияние помех по питанию. Дискретный ФНЧ уменьшает величину периодического джиттера выходного сигнала.

Данная архитектура синтезатора при всех достоинствах, обусловивших ее широкое применение в самых разнообразных проектах, включая наши собственные [5], имеет существенный недостаток, не позволяющий применить ее напрямую для генерации частоты видеоконтроллера. Речь идет о шаге установки частоты. При такой архитектуре он не может достигать требуемого для видеоконтроллеров значения 250 кГц. Так, при частотах выше 1 ГГц шаг в 250 кГц будет обеспечиваться при делении сигнала обратной связи делителем, имеющим разрядность не менее 12 бит. Как показывают расчеты и моделирование, низкая частота сигнала с выхода подобного делителя не обеспечивает устойчивой работы фазового детектора.

Для решения этой задачи иногда применяют дробный коэффициент деления сигнала в петле обратной связи. Такой подход описан, например, в работе [6], где используется схема с рандомизатором коэффициента деления. В статье [7] применяется дельтасигма-модулятор, переключающийся между десятью фазами сигнала в петле обратной связи. В этой же работе используется двухступенчатая схема генерации сигнала высокой частоты с дробным коэффициентом деления, показанная на рис. 6. Первая ступень, генератор пиксельной частоты (ГПЧ), построена на основе генератора десяти фаз и дельта-сигма-модулятора в цепи обратной связи. Вторая, блок умножения частоты (БУЧ), представляет из себя ФАПЧ с целочисленным фиксированным коэффициентом умножения, равным 7. Именно на эту величину умножается пиксельная частота при ее передаче по каналу для стандарта HDMI. Таким образом, в первой ступени синтезатора формируется сигнал относительно низкой частоты с точностью ее установки, укладывающейся в рамки стандарта, а вторая ступень преобразует этот сигнал в высокочастотный. Тем самым сложная задача разбивается на две более простые.

Однако данный подход имеет свои ограничения. Рассмотренная двухступенчатая архитектура синтезаторов разработана специалистами фирмы Samsung [7] и предназначена для использования в видеоконтроллерах дисплейных панелей со строго определенным разрешением. То есть ГПЧ обеспечивает только одну выходную частоту с высокой точностью, а БУЧ умножает ее в семь раз. В нашем же случае речь идет о проектировании видеоконтроллера для широкого спектра мониторов, в котором минимальная пиксельная частота отличается от максимальной приблизительно в пять раз. Такой широкий разброс опорных частот для второй ступени требует внесения изменений в архитектуру синтезатора.

Было решено взять за основу обеих ступеней разработанные ранее и описанные выше синтезаторы с целочисленным коэффициентом деления в цепи обратной связи. В этом случае формула для расчета выходной частоты приобретает следующий вид:

$$F_{OUT} = F_{REF} \cdot \frac{N_1}{M_1} \cdot \frac{N_2}{M_2} \cdot \frac{1}{P_1 \cdot P_2}, \tag{1}$$

где  $M_1$  и  $M_2$  обозначают коэффициенты деления опорной частоты в первой и второй ступенях соответственно,  $N_1$  и  $N_2$  — коэффициенты деления частоты в петлях обратной связи, а  $P_1$  и  $P_2$  — коэффициенты выходных делителей.

Наличие вдвое большего количества коэффициентов деления частот опорного сигнала и сигнала обратной связи по сравнению

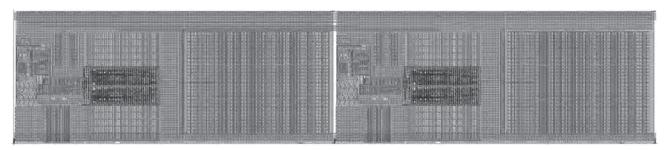

Рис. 4. Схема ГУН

с одноступенчатым синтезатором позволяет не только получать итоговый коэффициент преобразования частоты дробным с маленьким шагом, но и во многих случаях иметь большой набор вариантов для получения одного и того же значения выходной частоты. Последнее обстоятельство позволяет подбирать такие частоты опорного сигнала для второй ступени, величины которых лежат не в пятикратном, а в существенно более узком диапазоне для всех возможных пиксельных частот, обеспечивая тем самым минимальный джиттер выходного сигнала. При этом, например,  $F_{out}$  в диапазоне 500—501 М $\Gamma$ ц имеет следующий ряд возможных значений (в МГц): 500,00, 500,09, 500,15, 500,17, 500,22, 500,28, 500,29, 500,32, 500,39, 500,44, 500,47, 500,48, 500,52, 500,55, 500,60, 500,62, 500,69, 500,75, 500,77, 500,89, 500,96, 500,97, 501,00. Дополнительно следует отметить, что в целях обеспечения наибольшей устойчивости работы фазовых детекторов при расчетах и моделировании использовались значения коэффициентов М<sub>1</sub> и М<sub>2</sub>, не превышающие 10. Видно, что применение двухступенчатой схемы синтезаторов с целочисленными коэффициентами деления позволяет получить очень мелкий шаг изменения частоты, измеряющийся всего лишь десятками килогерц без использования дельта-сигма-модуляторов, рандомизаторов, фазовых интерполяторов и других вариантов получения дробного коэффициента деления в петле обратной связи. Топология разработанного синтезатора показана на рис. 7.

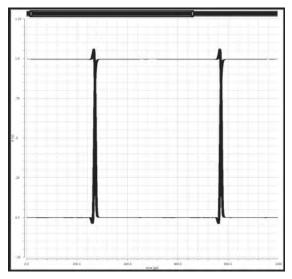

На рис. 8 представлена глазковая диаграмма сигнала с  $F_{\text{out}} = 1 \, \Gamma \Gamma \mu$ . Такое значение было выбрано исключительно в целях удобства построения и анализа диаграммы,

Рис. 5. Схема дифференциального буферного каскада ГУН

Рис. 6. Архитектура двухступенчатого синтезатора для видеоконтроллера

Рис. 7. Топология синтезатора

Рис. 8. Глазковая диаграмма сигнала с  $F_{out} = 1$   $\Gamma \Gamma u$

на других частотах картина аналогична с точки зрения джиттера. При этом коэффициенты деления были следующими:  $M_1 = M_2 = 10$ ,  $N_1 = 40$ ,  $N_2 = 80$ ,  $P_1 = 4$ ,  $P_2 = 1$ . А на рис. 9 показано начало процесса установления частоты ГУН первой ступени (500 МГц) и ГУН второй ступени (1 ГГЦ). Во второй ступени реализована схема детектора захвата частоты, которая срабатывает, если в течение 32 периодов сигнала опорной частоты для второй ступени фазовый детектор не выдавал сигнал изменения частоты вверх или вниз. Полностью процесс установления выходной частоты синтезатора занимает в зависимости от условий моделирования от 20 до 30 мкс.

Авторы считают, что в данной работе новым является применение двухступенчатой схемы ФАПЧ, в которой дробный коэффициент умножения опорной частоты получается при использовании целочисленных коэффициентов деления сигналов опорной частоты и обратной связи в каждой из ступеней. Такой подход позволяет использовать простую архитектуру ФАПЧ вместо применения фазовых интерполяторов, дельтасигма-модуляторов и рандомизаторов. При этом шаг изменения частоты измеряется десятками килогерц, что допускает использование предложенного синтезатора в схемах видеоконтроллеров с широким диапазоном поддерживаемых разрешений. Разработка модели и проведение компьютерных экспериментов проводились в среде проектирования Cadence. Полученные результаты подтвердили адекватность используемой модели и разработанного ФАПЧ. Синтезатор, использованный как прототип, успешно применялся ранее в нескольких проектах микропроцессоров, разработанных и изготовленных во ФГУ ФНЦ НИИСИ РАН.

Рис. 9. Процесс установления частоты ГУН первой и второй ступени

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН по теме №0065-2019-0004.

## **ЛИТЕРАТУРА**

- 1. John G. Maneatis. Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques // IEEE Journal of Solid-State Circuits, 1996. Vol. 31. № 11. P. 1723-1732.

- 2. Josh Carnes, Igor Vytyaz, Pavan Kumar Hanumolu, Kartikeya et al. Design and Analysis of Noise Tolerant Ring Oscillators Using Maneatis Delay Cells // IEEE International Conference, 2007. P. 494–497.

- 3. Jaeha Kim, Jeong-Kyoum Kim, Bong-Joon Lee, Namhoon Kim et al. A 20-GHz Phase-Locked Loop for 40-Gb/s Serializing Transmitter in 0.13-um CMOS // IEEE Journal of Solid-State Circuits, 2006. Vol. 41. № 4. P. 899-908.

- Adrian Maxim. A Low Reference Spurs 1-5 GHz 0.13 um CMOS Frequency Synthesizer Using a Fully-sampled Feed-Forward Loop Filter Architecture // IEEE Journal of Solid-State Circuits, 2007. Vol. 42. № 11. P. 2503-2514.

- 5. Агафонов А. Е. 1 ГГц синтезатор частоты со схемой автосмещения по технологии 65 нм. Электроника, микро- и наноэлектроника. Сборник научных трудов / Под ред. В.Я. Стенина. — М.: НИЯУ МИФИ, 2013. — С. 165-171.

- Chun-Huat Heng, Bang-Sup Song. A 1.8 GHz CMOS Fractional-N Frequency Synthesizer with Randomized Multi-Phase VCO // IEEE Custom Integrated Circuit Conference, 2002. P. 427-430.

- Jongshin Shin, Jaehyun Park, Bongjin Kim, Jongjae Rue et al. A 65nm 3.4 Gbps HDMI TX PHY with Supply-regulated Dual-tuning PLL and Blending Multiplexer // IEEE Custom Integrated Circuit Conference, 2008. P. 237-240.