# БИОМОРФНЫЙ НЕЙРОПРОЦЕССОР — ПРОТОТИП КОМПЬЮТЕРА НОВОГО ПОКОЛЕНИЯ, ЯВЛЯЮЩЕГОСЯ НОСИТЕЛЕМ ИСКУССТВЕННОГО ИНТЕЛЛЕКТА. ЧАСТЬ 1

# BIOMORPHOUS NEUROPROCESSOR – PROTOTYPE OF A NEW GENERATION COMPUTER BEING A CARRIER OF ARTIFICIAL INTELLIGENCE. PART 1

С.Ю.Удовиченко $^*$ , д.ф.-м.н., проф., (ORCID: 0000-0003-3583-7081), А.Д.Писарев $^*$ , к.т.н., доц., (ORCID: 0000-0002-5602-3880), А.Н.Бусыгин $^*$ , аспирант, (ORCID: 0000-0002-3439-8067), А.Н.Бобылев $^*$ , заведующий лабораторией, (ORCID: 0000-0001-5488-8736) / udotgu@mail.ru

S.Yu.Udovichenko\*, Doct. of Sc. (Physics and Mathematics), Prof., A.D.Pisarev\*, Cand. of Sc. (Technical), Docent, A.N.Busyqin\*, Post-Graduate, A.N.Bobylev\*, Head of Laboratory

DOI: 10.22184/1993-8578.2020.13.7-8.466.475

Получено: 27.08.2020 г.

Биоморфный нейропроцессор реализует аппаратную импульсную нейросеть для традиционных задач обработки информации, а также для воспроизведения работы кортикальной колонки мозга. Ключевыми узлами аппаратной нейросети являются запоминающая и логическая матрицы, разработанные на основе нового компонента наноэлектроники – комбинированного мемристорнодиодного кроссбара, обладающие высокой интеграцией элементов и энергоэффективностью по сравнению с известными нейропроцессорами и отдельными матрицами. Представлены концепция биоморфного нейропроцессора, описание нейросети, построенной на основе оригинальной программной модели нейрона и адаптированной к аппаратной части нейропроцессора, а также нанотехнология изготовления мемристорно-диодного кроссбара и результаты исследования его электрофизических свойств.

A biomorphic neuroprocessor implements a hardware impulse neural network for traditional information processing tasks, as well as for reproducing the work of the cortical column of the brain. The key nodes of the hardware neural network are the memory and logic matrices, developed on the basis of a new component of nanoelectronics – a combined memristor-diode crossbar, which have a high integration of elements and energy efficiency compared to known neuroprocessors and separate matrices. The concept of a biomorphic neuroprocessor, a description of a neural network built on the basis of an original software model of a neuron and adapted to the hardware of the neuroprocessor, as well as nanotechnology for manufacturing a memristor-diode crossbar and the results of a study of its electrophysical properties are presented.

## ВВЕДЕНИЕ

Искусственные нейронные сети появились как модель обработки информации в простых нейронах. Такой информационный подход используется сейчас в системах машинного обучения, распознавания паттернов в видео- и аудиоинформации и

других системах со слабым искусственным интеллектом. Принятие решений в таких устройствах происходит в результате анализа информации, хранящейся в блоках памяти, и выбора наиболее правдоподобного решения на основе заложенных ассоциаций [1]. Обзор нейросетей на основе

<sup>\*</sup> Тюменский государственный университет / University of Tyumen.

# **EQUIPMENT FOR NANOINDUSTRY**

простых нейронов, описание их архитектуры и процедур обучения представлен в [2]. Другое применение искусственных нейросетей предназначено для моделирования работы отдельных частей мозга. Моделирование биологических нейросетей с большим количеством нейронов требует огромных вычислительных мощностей и сейчас выполняется программно на суперкомпьютерах. Особое внимание уделяется так называемой кортикальной колонке (гиперколонке) универсального элемента неокортекса [3]. Миниколонки предназначены для распознания элементарных признаков образа и обеспечивают оперативную память, а гиперколонки служат для комплексного объединения элементарных признаков.

Существующие программно-аппаратные нейропроцессоры работают как ускорители отдельных математических операций нейросети с точечными (простыми) нейронами и построены как на классической КМОП-логике [4, 5], так и с применением мемристорных кроссбаров [6, 7]. В России по проектным нормам 65 нм в 2019 году изготовлен первый отечественный нейросетевой ускоритель NCore, предназначенный для машинного обучения, основанного на математическом аппарате глубоких нейронных сетей. Аппаратные импульсные нейронные сети, построенные на основе биоморфмной модели нейрона, потребляют меньше энергии, чем традиционные сверточные нейронные сети на точечных нейронах, а также обладают более простой процедурой обучения [8].

Образцами импульсных нейропроцессоров являются TrueNorth [9], Brainchip Akida [8, 10] и Intel Loihi [11], изготовленные на транзисторах по КМОПтехнологии. В последних двух нейропроцессорах уже реализованы механизмы самообучения импульсных нейросетей. Применение в дальнейшем в таких нейропроцессорах мемристоров в качестве синапсов обеспечит значительное сокращение числа транзисторов, благодаря реализации в мемристоре множества резистивных состояний.

Концепция нейроморфных устройств, являющихся комбинацией КМОП-логики и мемристоров, впервые предложена в [12, 13] и реализована в виде автономного устройства в [14]. Существующие аппаратные средства в виде запоминающих [15-18] и логических матриц [19-22] на мемристорах выполняют узкоспециальные функции.

В [23, 24] представлена разработка биоморфного нейропроцессора на основе мемристорно-диодного кроссбара, реализующего аппаратную импульсную нейросеть на основе оригинальных биоморфных электрической и программной [25] моделей нейрона.

Эта аппаратная биоморфная нейросеть способна воспроизводить работу кортикальной колонки мозга или ее фрагмента. В качестве ключевых узлов аппаратной части нейропроцессора используются сверхбольшие запоминающая матрица с ячейками из комплементарных мемристоров 1D2M [26] и логическая матрица с ячейками 1D1M [27], представляющие собой массив синапсов и задающие вес и маршрут связи между нейронами соответственно. Указанные матрицы являются сверхбольшими потому, что каждый нейрон в сети может обладать большим количеством синаптических связей. При разработке этих матриц среди селективных элементов выбор сделан в пользу диода Зенера по следующим причинам: низкое напряжение пробоя, используемое для перепрограммирования мемристоров; как унифицированный элемент он же используется в логической матрице для реализации диодной логики; имеет размер, соизмеримый с размером мемристора.

Исходя из большой архитектуры нейропроцессора и соответствующего большого количества элементов в электрической схеме, к его узлам предъявляются общие требования: высокая степень интеграции элементов при объединении их в сверхбольшую матрицу; минимизация площади, которую занимает ячейка матрицы на кристалле; высокие быстродействие и энергоэффективность. Этим требованиям удовлетворяет разработанный биоморфный нейропроцессор, в котором продемонстрированы высокие интеграция элементов [28] и энергоэффективность сверхбольших запоминающей [26] и логической [27] матриц, построенных на основе комбинированного мемристорно-диодного кроссбара, по сравнению с известными нейропроцессорами и отдельными матрицами. Такая эффективность достигнута за счет применения смешанных аналогово-цифровых вычислений, в том числе с помощью мемристоров, интегрированных в мемристорнодиодные кроссбары.

В биоморфном нейропроцессоре продемонстрированы высокие интеграция элементов и энергоэффективность по сравнению с известными нейропроцессорами и отдельными матрицами. Такая эффективность достигнута за счет применения смешанных аналогово-цифровых вычислений, в том числе с помощью биполярных мемристоров, интегрированных в комбинированные мемристорно-диодные кроссбары. Проведено SPICE-моделирование процессов обработки сигналов в цифровом режиме: сложение выходных импульсов нейронов в запоминающей матрице; их маршрутизация на синапсы других нейронов в логической матрице [23], ассоциативного самообучения, а также умножение матрицы

# Оборудование для наноиндустрии

на вектор, которое применяется в запоминающей матрице и во входном блоке нейропроцессора при обработке видео и звуковых сигналов [29].

Ассоциативное самообучение и формирование новой ассоциации в нейросети с мемристорными синапсами по правилу Хебба аппаратно реализованы на дискретных мемристорах в работах [30–34]. Однако, предложенные электрические цепи аппаратной реализации ассоциативной памяти не могут быть использованы для построения большой аппаратной нейросети с высокими интеграцией элементов и энергоэффективностью. Причиной является отсутствие интеграции мемристоров в кроссбары и наличие в схемах нейронов и синапсов большого числа активных электронных элементов с высоким энергопотреблением.

В процессе аппаратной реализации биоморфного нейропроцессора в мемристорно-диодном кроссбаре, изготовленном с помощью нанотехнологического комплекса "НаноФаб-100" и электронной литографии, проведена обработка информации для запоминающей и логической матриц. Впервые в процессе ассоциативного самообучения продемонстрирована генерация новой ассоциации (нового знания) в мемристорно-диодном кроссбаре, в отличие от самообучения в существующих нейросетях с синапсами на базе дискретных мемристоров [35].

Разработку нейропроцессоров на основе мемристоров и мемристорных кроссбаров тормозит то обстоятельство, что разрабатываемые твердотельные мемристоры на оксидах переходных металлов пока имеют невысокую стабильность и воспроизводимость электрических характеристик.

Однако предложенный биоморфный нейропроцессор не подвержен этому обстоятельству (недостатку). Распределенный характер биоморфной нейросети снижает требования к воспроизводимости и стабильности характеристик мемристоров и повышает отказоустойчивость схемы нейропроцессора. Кроме этого, в аппаратную реализацию нейросети можно добавить электрическую схему, которая будет воспроизводить работу астроцита (одного из видов глиальных клеток мозга) путем увеличения проводимости оставшихся мемристорных синапсов при обнаружении поврежденного [36, 37]. Это еще повысит отказоустойчивость схемы нейропроцессора и дополнительно увеличит биоморфность нейросети. Еще одна возможность коррекции поврежденного мемристорного синапса состоит в увеличении возбудимости пресинаптического нейрона путем снижения порога активации или увеличения весов его возбуждающих синапсов.

В обзоре представлены этапы разработки биоморфного нейропроцессора, включающие электрическую схему, топологию и нанотехнологию изготовления его отдельных узлов, подтверждение их работоспособности с помощью SPICE-моделирования и демонстрации процессов обработки информации в мемристорно-диодном кроссбаре, являющемся основой аппаратной реализации нейропроцессора.

# КОНЦЕПЦИЯ БИОМОРФНОГО НЕЙРОПРОЦЕССОРА И БИОМОРФНАЯ НЕЙРОСЕТЬ

Под биоморфным нейропроцессором подразумевается аппаратное средство, представляющее собой программно-аппаратную нейросеть, построенную на основе биологической электрической модели нейрона Ходжкина – Хаксли [38, 39]. Программная часть такой реализации отвечает за возможность программирования синаптических связей между нейронами нейросети, а также ввод и вывод информации. Все основные функции: взвешивание и суммирование импульсов напряжения (умножение на вес связи), генерация потенциала действия при превышении порога, маршрутизация импульсов между нейронами – выполняются с помощью аппаратного средства. С этой точки зрения, такая реализация ближе к полностью аппаратной.

# Подходы в аппаратной реализации нейропроцессора

В концепции аппаратной реализации нейропроцессора предлагаются два подхода. Первый подход направлен на уменьшение числа элементов электроники при использовании аналоговых вычислений для синапсов и нейронов. Схема нейропроцессора в этом случае предполагает наличие запоминающей матрицы, блока нейронов и маршрутизатора на основе логической матрицы. Аналоговая запоминающая матрица является массивом синапсов и, помимо запоминания информации, производит часть расчетов нейросети в виде взвешенного суммирования входных импульсов нейронов. Нейронный блок производит оставшуюся часть вычислений, относящихся к процессам зарядки мембраны нейрона выходными импульсами запоминающей матрицы и генерации выходных импульсов нейронов при превышении порога активации. Маршрутизатор отвечает за перенаправление выходных сигналов нейронов на синапсы в запоминающей матрице. Входное устройство нейропроцессора предназначено для первичной обработки звуковой и видеоинформации путем ее сжатия и кодирования в виде отдельных импульсов, в том числе подобных биоморфным импульсам мозга. Выходное устройство осуществляет преобразование

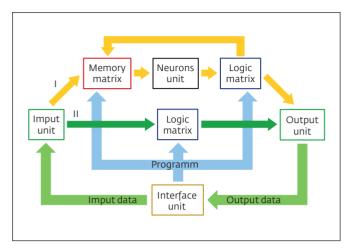

Рис.1. Функциональная схема нейропроцессора: вариант I – с использованием запоминающей матрицы для синапсов и логической матрицы в качестве маршрутизатора; вариант II – на основе универсальной логической матрицы в отсутствие запоминающей матрицы

Fig.1. Functional diagram of the neuroprocessor: I - using a memory matrix for synapses and a logical matrix as a router; II - based on a universal logical matrix in the absence of a storage matrix

информации об активации нейронов в цифровой двоичный код, ее сжатие и передачу на интерфейсный блок.

Второй подход основан на унификации элементов электроники, топологии и технологии изготовления за счет использования одной и той же электрической схемы универсальной логической матрицы во всех функциональных блоках нейропроцессора.

Универсальная электрическая схема логической матрицы может выполнять расчет связей нейросети в отсутствие отдельной запоминающей матрицы. На основе собственных логических функций она выполняет умножение матрицы на вектор путем последовательных конъюнкций с инверсией; в качестве маршрутизатора направляет выходные импульсы нейронов на синапсы других нейронов; в качестве части входного устройства нейропроцессора выполняет первичную обработку звуковых и видеосигналов, включающую в себя сжатие и кодирование информации в импульсы; в качестве части выходного устройства осуществляет преобразование информации об активации нейронов в цифровой двоичный код и передачу на интерфейсный блок.

Два варианта функциональной схемы нейропроцессора, в которой отражены основные узлы, представлены на рис.1.

Достоинства реализации нейропроцессора на основе второго подхода проявляются в более высоком быстродействии и энергоэффективности,

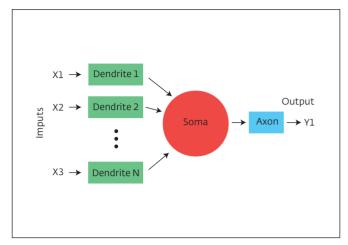

Рис.2. Схема биоморфной модели нейрона Fig. 2. Diagram of a biomorphic neuron model

обусловленные представлением сигналов в цифровой форме, и более простой технологии изготовления аппаратной базы нейропроцессора за счет использования унифицированных элементов во всех блоках.

# Нейросеть на основе оригинальной биоморфной модели нейрона

Для обработки информации в сверхбольшой нейросети, предназначенной для нейропроцессора с ограниченными вычислительными ресурсами, построена максимально упрощенная программная модель нейрона (с точки зрения времени расчета), но без существенной потери точности. Из таких относительно простых нейронов, описываемых биоморфной моделью, построена нейросеть [25], способная моделировать работу кортикоморфной колонки с определенными функциями, подобно кортикальным колонкам мозга. Комбинируя кортикоморфные колонки, в дальнейшем можно реализовать модель коры головного мозга, которая не будет требовать для расчета больших вычислительных мощностей, поскольку программные нейросетевые расчеты будут заменены на аппаратную реализацию.

На рис.2 представлена оригинальная биоморфная модель нейрона, которая отличается от информационных моделей более сложным устройством синапса, а от биологических моделей - заменой дифференциальных уравнений, описывающих изменение потенциала во времени на мембране нейрона, на явные рекуррентные соотношения путем аппроксимации экспериментальных данных в кортикальном нейроне. И, как следствие, переходом от spiking-кодирования информации на кодирование средней частотой потенциалов действия за

# Оборудование для наноиндустрии

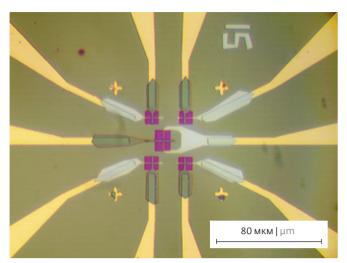

Рис.3. Микрофотография с оптического микроскопа мемристорного кроссбара на основе смешанного оксида металлов  ${\rm Ti}_{\bf x}{\rm Al}_{1-{\bf y}}{\rm O}_{\bf y}$

Fig.3. Micrograph from a memristor optical microscope crossbar based on mixed  $Ti_xAl_{1-x}O_v$  metal oxide

шаг моделирования. Такой подход обеспечивает и повышает эффективность расчета нейросети в автономном аппаратном средстве с ограниченными вычислительными ресурсами.

Модель состоит из трех отдельных функциональных частей: дендритов, сомы и аксона и позволяет реализовывать любые соединения между функциональными частями разных нейронов, что придает большую гибкость архитектуре нейросети. Для проверки работоспособности модели нейрона проведена симуляция тестовой нейросети, построенной по принципам последовательной сборки из функциональных блоков и начального задания связей на основе экспериментальных данных нейрофизиологии, выполняющей простую ассоциацию. Показано, что кодирование передаваемой информации импульсами, подобными биологическим, позволяет использовать мемристоры для расчета рекуррентных выражений, описывающих изменение количества рецепторов на мембране дендрита.

Адаптация к нейропроцессору биоморфной нейросети по существу сводится к адаптации программной биоморфной модели нейрона, поскольку информация о связях между нейронами переносится непосредственно. Такая адаптация заключается в пересчете коэффициентов в рекуррентных выражениях биоморфной модели нейрона через электрические параметры узлов нейропроцессора. Для этого произведены следующие процедуры:

1. соотнесены состояния комплементарных мемристоров с числом рецепторов нейромедиаторов;

- 2. установлена связь скорости затухания остаточного постинаптического потенциала в дендрите со скоростью разряда суммирующего конденсатора в электрической схеме нейрона (см. рис.4);

- 3. пересчитаны коэффициенты скоростей синтеза и распада рецепторов в синапсе;

- 4. подобрана величина порогового напряжения генерации импульса в аппаратном нейроне, соответствующая порогу активации нейрона в биоморфной модели.

Разработанная программная биоморфная модель нейрона, сформулированные принципы построения нейросети на ее основе, а также замена синапсов в нейросети на мемристоры позволяют построить сверхбольшую биоморфную нейросеть, которая может воспроизводить работу кортикальной колонки мозга на автономном аппаратном средстве – биоморфном нейропроцессоре.

# НАНОТЕХНОЛОГИЯ ИЗГОТОВЛЕНИЯ И ЭЛЕКТРИЧЕСКИЕ СВОЙСТВА КОМБИНИРОВАННОГО МЕМРИСТОРНО-ДИОДНОГО КРОССБАРА

Новый компонент наноэлектроники – комбинированный мемристорно-диодный кроссбар является основой запоминающей и логической матриц. Ячейка запоминающей матрицы представляет собой двухслойное соединение комплементарных биполярных мемристоров и одного разделяющего диода Зенера, а ячейка логической матрицы – одного мемристора и диода. Применение диода Зенера позволяет уменьшить деградацию выходного сигнала из-за влияния соседних ячеек.

#### Изготовление мемристоров по технологии "кроссбар"

Наиболее перспективны для создания запоминающей и логической матриц являются мемристоры на основе оксидов переходных металлов. В мемристоре между предельными высокопроводящим и низкопроводящим состояниями имеется множество промежуточных состояний с разной проводимостью. Эти состояния можно использовать в процессах ассоциативного самообучения нейросети на основе мемристорных синапсов и одновременной обработки входных импульсов, заключающейся в их взвешивании и суммировании в запоминающей матрице. Чем шире диапазон резистивного переключения мемристора, тем больше можно реализовать синаптических связей с помощью этого мемристора в нейропроцессоре.

Технология изготовления и электрические свойства мемристорного кроссбара без диода представлены в [40–42]. Определены электрические свойства твердотельного мемристора, подобные свойствам

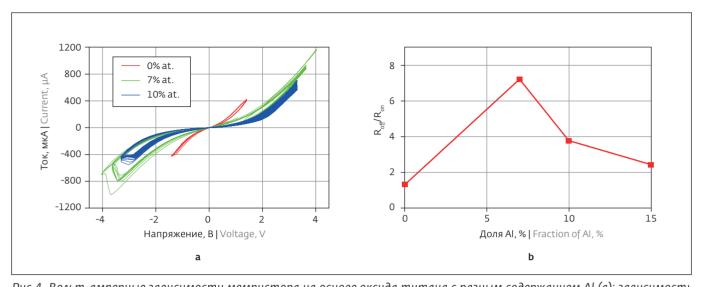

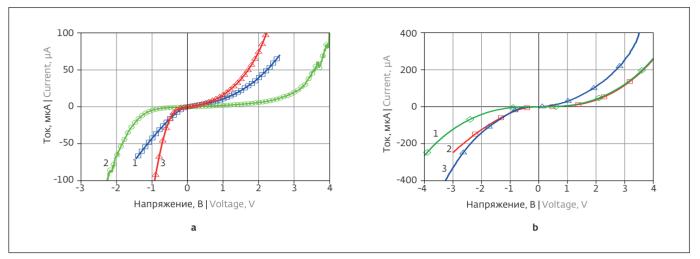

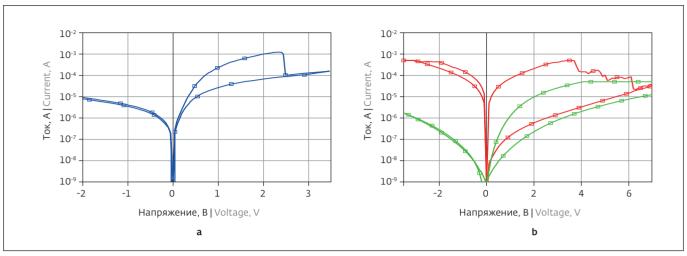

Puc.4. Вольт-амперные зависимости мемристора на основе оксида титана с разным содержанием AI (a); зависимость отношения сопротивлений  $R_{off}$  и  $R_{on}$  при напряжении считывания 0,2 B от мольной доли AI (b) Fig.4. Current-voltage dependences of a memristor based on titanium oxide with different content of AI (a); dependence of the resistance ratio  $R_{off}$  and  $R_{on}$  at a readout voltage of 0.2 V of the AI mole fraction (b)

живого синапса при распространении нервного импульса и указана возможность использования мемристора, как суммирующего элемента искусственного нейрона.

Однако такие мемристоры обладают нестабильностью напряжений переключения и предельных сопротивлений. Проблему высокого разброса значений сопротивлений можно решить путем легирования оксида переходного металла. Наибольшая стабильность была достигнута при циклической нагрузке в структуре  $TiN/Ti_{0,92}$   $Al_{0,08}O_y/TiN$ , изготовленной методом магнетронного распыления, с отклонениями значений сопротивления мемристора в открытом  $\Delta Ron = 3,3\%$  и закрытом  $\Delta Roff = 15,7\%$  состояниях [40].

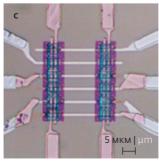

Изготовление мемристорного кроссбара проводилось в магнетронном модуле, входящем в нанотехнологический комплекс NT-MDT "НаноФаб-100" [41, 42]. Пленка смешанного оксида металлов осаждалась при одновременном распылении двух катодов из Ті и Al. Мемристоры изготовлены по технологии кроссбар (рис.3) путем последовательного напыления пленок через маски электронного резиста (РММА), выполненные на электронном микроскопе JSM-6510LV-EDS.

Результаты измерений вольт-амперных характеристик свидельствуют (рис.4), что внесение Al в оксид титана улучшает электрофизические характеристики мемристора, причем существует оптимальная мольная доля Al, при которой достигается максимальное отношение R сопротивлений мемристора

в низкопроводящем Roff и высокопроводящем Ron состояниях. Внесение Al в  $TiO_2$  на уровне 7 ат.% увеличивает R с 1,3 до 7,2. Дальнейшее увеличение доли Al не приводит к росту отношения R.

Определенный с помощью рентгеновской фотоэлектронной спектроскопии элементный состав пленки смешанного оксида металлов показал, что метод реактивного магнетронного осаждения обеспечивает отсутствие примесей и равномерное распределение элементов по толщине пленки смешанного оксида, в отличие от метода атомно-слоевого осаждения [43, 44]. Это способствует равномерному распределению электрического поля между проводниками мемристора и, как следствие, приводит к увеличению стабильности вольт-амперных характеристик при циклической нагрузке.

Можно ожидать, что в мемристорах на оксидах других переходных металлов Hf и Zr с добавлением примеси Sc, Y, Lu также будет наблюдаться оптимальная доля примеси, соответствующая максимально повышенному отношению сопротивлений в низкопроводящем и высокопроводящем состояниях.

## Изготовление полупроводниковых диодных слоев

Требования к основным характеристикам диода Зенера следующие: сопротивление диода в закрытом состоянии должно быть максимально возможным, а в открытом состоянии и при пробое – как можно меньшим; напряжение открытия диода при прямом смещении должно быть минимальным, а

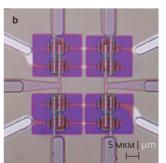

Рис.5. ВАХ диодов: a − p-Si / ZnO $_X$  при разной мольной доли Zn (1 − 56,68%, 2 − 61,75%, 3 − 72,75%) и c удельным conpomuвлением p-Si, равным 0,275 Oм  $\cdot$  cм; b − p-Si / n-Si (1) и p-Si / Zn $_{0,62}$  O $_{0,38}$  c разным удельным conpomuвлением p-Si: 2 − 0,066 Oм  $\cdot$  cм и 3 − 0,275 Ом  $\cdot$  cм

Fig.5. I-V characteristics of diodes:  $a-p-Si/ZnO_x$  at different molar fractions of Zn (1 – 56.68%, 2 – 61.75%, 3 – 72.75%) and with a specific resistance of p-Si equal to 0.275 Ohm·cm; b-p-Si/n-Si (1) and p-Si /  $Zn_{0.62}$   $O_{0.38}$  with different resistivity p-Si: 2-0.066 Ohm·cm and 3-0.275 Ohm·cm

напряжение обратимого пробоя, соответственно, должно быть больше напряжения информационных импульсов.

На рис.5 представлены вольт-амперные характеристики диодов, изготовленных с помощью реактивного магнетронного распыления катодов с легированным кремнием p-Si, n-Si и напылением оксида цинка  ${\rm ZnO_x}$  на подложку из кремния с разным уровнем легирования p-Si. Видно, что эти требования лучше выполняются в диоде p-Si/n-Si.

Из рис.5а следует, что с увеличением мольной доли цинка нелинейность ВАХ растет, достигает максимума при 61,75 ат.%, а затем падает. Увеличение доли цинка приводит к росту числа основных носителей заряда (электронов), что увеличивает нелинейность характеристики. Однако

слишком большая концентрация цинка приводит к шунтированию p-n-перехода, что, в свою очередь, приводит к выравниванию вольт-амперной характеристики. Таким образом, существует оптимальная мольная доля Zn, которая дает наилучшие характеристики диода p-Si / ZnO.

### Изготовление комбинированного кроссбара

Нанотехнология изготовления лабораторного комбинированного мемристорно-диодного кроссбара, являющегося основой запоминающей и логической матриц, представлена в [35, 45–47]. Сделан выбор материалов мемристора и полупроводниковых слоев диода с целью получения их оптимальных электрических характеристик. Показано, что метод магнетронного распыления является унифицированным

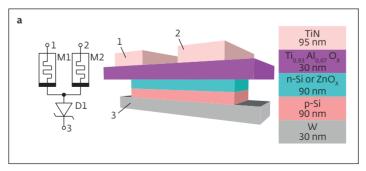

Puc.6. Электрическая схема и топология ячейки 1D2M: a – микрофотографии изготовленных массивов со структурами: b – W / p-Si /  $Ti_{0,93}$ Al $_{0,07}$ O $_x$  / TiN (b), c – W / p-Si / ZnO /  $Ti_{0,93}$ Al $_{0,07}$ O $_x$  / TiN (c)

Fig.6. Electrical diagram and topology of 1D2M cell: a – micrographs of the fabricated arrays with structures: b – W / p-Si / n-Si /  $Ti_{0,93}Al_{0,07}O_x$  / TiN, c – W / p-Si / ZnO /  $Ti_{0,93}Al_{0,07}O_x$  / TiN

Puc.7. Сравнение BAX ячеек кроссбаров: a – u3 [11]; b – зеленая кривая для  $TiN/Ti_{0,93}AI_{0,07}O_x/p$ -Si/n-Si/W u красная для  $TiN/Ti_{0,93}AI_{0,07}O_x/p$ -Si/2nO/W

Fig.7. Comparison of the I–V characteristics of the cells of crossbars: a – from [11]; b – green curve for TiN /  $Ti_{0.93}AI_{0.07}O_x$  / p-Si / n-Si / W and red for TiN /  $Ti_{0.93}AI_{0.07}O_x$  / p-Si / ZnO / W

для изготовления диодов и мемристоров. Таким образом, все слои комбинированного мемристорнодиодного кроссбара, включая проводящие дорожки, могут быть изготовлены в одном технологическом цикле.

Электрическая схема и топология ячейки 1D2M, а также микрофотографии кроссбар-массивов этих ячеек с двумя разными диодами приведены на рис.2 [48].

На рис.6 хорошо видны взаимно перпендикулярные проводники кроссбара. Пленка мемристорного слоя  ${\rm Ti}_{0,93}{\rm Al}_{0,07}{\rm O}_{\rm x}$  имеет фиолетовый цвет, верхний слой диода n-Si (рис.6b), расположенный под мемристорным слоем, имеет бежевый цвет, а верхний слой диода  ${\rm ZnOx}$  (рис.6c) – голубой цвет.

Вольт-амперные характеристики ячеек комбинированного мемристорно-диодного кроссбара представлена на рис.7.

На зеленой кривой рис.7b резкого перехода RESET не видно из-за принудительного ограничения максимального тока. Отличие в ширине гистерезиса на рис.4a и 7b обусловлено различием материала одного из электродов мемристора. В первом случае материалом электродов мемристора является TiN, а во втором – TiN и n-Si.

Большое сопротивление закрытого диода приводит к стягиванию гистерезиса в обратной ветви вольт-амперной характеристики ячейки, поскольку вклад сопротивления диода преобладает над вкладом малого сопротивления мемристора в их общей ВАХ. Такой же эффект наблюдается в кроссбаре [49]

(рис.7а) с униполярным мемристором на основе смешанного оксида никеля и титана и диодом p-CuO / n-ZnO:In. Как видно из рис.7b ячейка с диодом p-Si / n-Si обладает лучшим выпрямляющим свойством по сравнению с ячейкой с диодом p-Si / ZnO<sub>x</sub>, поскольку ток в открытой ячейке при положительном напряжении значительно выше, чем при отрицательном напряжении. Высокое выпрямляющее свойство ячейки необходимо для функционирования диодной логики в логической матрице и при записи состояний мемристоров в запоминающей и логической матрицах.

#### ЛИТЕРАТУРА / REFERENCES

- 1. **Schuman C.D.**, **Potok T.E.**, **Patton R.M.**, et al. A Survey of Neuromorphic Computing and Neural Networks in Hardware. arXiv preprint, 2017, 1705.06963.

- 2. **Schmidhuber J.** Deep Learning in Neural Networks: An Overview. Neural Networks, 2015, 61, pp. 85–117.

- 3. **Silberberg G., Gupta A., Markram H.** Stereotypy in neocortical microcircuits. Trends in Neurosciences, 2002, 25, no. 5, pp. 227–230.

- 4. **Ionica M.H.**, **Gregg D.** The Movidius Myriad Architecture's Potential for Scientific Computing. IEEE Micro, 2015, 35, no. 1, pp. 6–14.

- 5. **Jouppi N.**, **Young C.**, **Patil N.**, **Patterson D.** Motivation for and Evaluation of the First Tensor Processing Unit. IEEE Micro, 2018, 38, no. 3, pp. 10–19.

# Оборудование для наноиндустрии

- 6. Shafiee A., Nag A., Muralimanohar N., et al. ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars. ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), 2016, pp. 14-26.

- 7. Ankit A., Hajj I.E., Chalamalasetti S.R., et al. PUMA: A Programmable Ultra-efficient Memristor-based Acceleratorfor Machine Learning Inference.—Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2019, pp. 715–731.

- 8. Akida Neuromorphic System-on-Chip [Online]. Available: https://www.brainchipinc.com/products/akida-neuromorphic-system-on-chip

- 9. **Merolla P.A.**, **Arthur J.V.**, **Alvarez-Icaza R.**, et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science, 2014, 345, pp. 668–672.

- 10. AJ Van Der Made P., Viejo A., Mankar A.S., Viejo M. Neural Processor based accelerator system and method. US Patent № 2017/0024644 A1, 2017.

- 11. **Davies M., Srinivasa N., Lin T.,** et al. Loihi: A Neuromorphic Manycore Processor with On-Chip Learning. IEEE Micro, 2018, 38, no. 1, pp. 82–99.

- 12. **Prezioso M., Merrikh-Bayat F., Hoskins B.D.,** et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature, 2015, 521, pp. 61–64.

- 13. **Kim K.**, **Gaba S.**, **Wheeler D.**, et al. A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Letters, 2012, 12, pp. 389–395.

- 14. Bobylev A.N., Busygin A.N., Pisarev A.D., Udovichenko S.Yu., Filippov V.A. Neuromorphic coprocessor prototype based on mixed metal oxide memristors. International Journal of Nanotechnology, 2017, v. 14, no. 7/8, pp. 698–704.

- 15. **Bennet C.**, **Querlioz D.**, **Klein J.** Spatio-temporal Learning with Arrays of Analog Nanosynapses. IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), 2017, pp. 125–130.

- 16. Yao P., Wu H., Gao B., et al. Online Training on RRAM based Neuromorphic Network: Experimental Demonstration and Operation Scheme Optimization. IEEE Electron Devices Technology and Manufacturing Conference (EDTM), 2017, pp. 182–183.

- 17. **Li C.**, **Belkin D.**, **Li Y.**, et al. Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nature Communications, 2018, 9, pp. 2385.

- 18. **Ielmini D.** Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses and

- neural networks. Microelectronic Engineering, 2018, 190, pp. 44–53.

- 19. **Levy Y.**, **Bruck J.**, **Cassuto Y.**, et al. Logic operations in memory using a memristive Akers array. Microelectronics Journal, 2014, 45, pp. 1429–1437.

- 20. Li C., Hu M., Li Y., et al. Analogue signal and image processing with large memristor crossbars. Nature electronics, 2018, 1, no. 1, pp. 52–59.

- 21. **Teimoori M.**, **Amirsoleimani A.**, **Ahmadi A.**, **Ahmadi M.** A 2M1M Crossbar Architecture: Memory. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26, no. 1, pp. 2608–2618.

- 22. **Zhang Y., Shen Y., Wang X., Cao L.** A Novel Design for Memristor-Based Logic Switch and Crossbar Circuits. IEEE Transactions on Circuits and Systems I: Regular Papers, 2015, 62, no. 5, pp. 1402–1411.

- 23. Pisarev A.D., Busygin A.N., Udovichenko S.Y., Maevsky O.V. A biomorphic neuroprocessor based on a composite memristor-diode crossbar. Microelectronics Journal, 2020, 102, 104827.

- 24. Udovichenko S.Yu., Pisarev A.D., Busygin A.N., Maevsky O.V. Neuroprocessor based on combined memristor-diode crossbar. Nanoindustry, 2018, no. 5, pp. 344–355.

- 25. Filippov V.A., Bobylev A.N., Busygin A.N., Pisarev A.D., Udovichenko S.Y. A biomorphic neuron model and principles of designing a neural network with memristor synapses for a biomorphic neuroprocessor. Neural Computing and Applications, 2020, 32, pp. 2471–2485.

- Pisarev A.D., Busygin A.N., Udovichenko S.Yu., Maevsky O.V. 3D memory matrix based on a composite memristor-diode crossbar for a neuromorphic processor. – Microelectronic Engineering, 2018, 198, pp. 1–7.

- 27. Udovichenko S., Pisarev A., Busygin A., Maevsky O. 3D CMOS memristor nanotechnology for creating logical and memory matrices of neuroprocessor. Nanoindustry, 2017, no. 5, pp. 26–34.

- 28. Pisarev A.D., Busygin A.N., Bobylev A.N., Udovichenko S.Yu. High element integration in logical and memory matrices of neuroprocessor by applying composite memristor-diode crossbar. International journal of nanotechnology, 2019, 16, no. 1/2/3, pp. 182–186.

- 29. Pisarev A.D., Busygin A.N., Bobylev A.N., Udovichenko S.Yu. Operation principle and fabrication technology of the neuroprocessor input unit on the basis of the memristive logic matrix. International journal of nanotechnology, 2019, 16, no. 6–10, pp. 596–601.

- 30. Wang Z., Wang X. A Novel Memristor-Based Circuit Implementation of Full-Function Pavlov Associa-

# **EQUIPMENT FOR NANOINDUSTRY**

- tive Memory Accorded with Biological Feature. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018, 65, no. 7, pp. 2210–2220.

- 31. Yang L., Zeng Z., Huang Y., Wen S. Memristor-Based Circuit Implementations of Recognition Network and Recall Network with Forgetting Stages. IEEE Transactions on Cognitive and Developmental Systems, 2018, 10, no. 4, p. 1133–1142.

- 32. **Wang Z.**, **Rao M.**, **Han J.** et al. Capacitive neural network with neuro-transistors. Nature Communications, 2018, 9, 3208.

- 33. **Zhang X.**, **Long K.** Improved Learning Experience Memristor Model and Application as Neural Network Synapse. IEEE Access, 2019, 7, p. 15262–15271.

- 34. Minnekhanov A.A., Emelyanov A.V., Lapkin D.A., et al. Parylene Based Memristive Devices with Multilevel Resistive switching for Neuromorphic Applications. Scientific Reports, 2019, 9, 10800.

- 35. Писарев А.Д., Бусыгин А.Н., Бобылев А.Н., Губин А.А., Удовиченко С.Ю. Исследование электрофизических свойств комбинированного мемристорно-диодного кроссбара, являющегося основой для аппаратной реализации биоморфного нейропроцессора. Вестник Тюменского государственного университета. Физико-математическое моделирование. Нефть, газ, энергетика, 2020, 6, № 3, с. 93-109.

- 36. Liu Junxiu, Harkin Jim, Maguire Liam P., McDaid Liam J., Wade John, Spanner J. A Self-Repairing Spiking Neural Network Hardware Architecture. IEEE Transactions on Neural Networks and Learning Systems, 2017, 29, no. 4, pp. 1287–1300.

- **37.** Liu Junxiu, Mcdaid Liam J., Harkin Jim, et al. Exploring Self-Repair in a Coupled Spiking Astrocyte Neural Network. IEEE Transactions on Neural Networks and Learning Systems, 2018, 30, no. 3, pp. 865–875.

- 38. **Brette R.**, **Gerstner W.** Adaptive Exponential Integrate-and-Fire Model as an Effective Description of Neuronal Activity. Journal of neurophysiology, 2005, 94, pp. 3637–3642.

- 39. **Hodgkin A.L.**, **Huxley A.F.** A quantitative description of membrane current and its application to conduction and excitation in nerve. Journal of Physiology, 1952, 117, no, 4, pp. 500–544.

- 40. **Bobylev A.N.**, **Udovichenko S.Yu**. The electrical properties of memristor devices TiN/Ti<sub>x</sub> Al<sub>1-x</sub> O<sub>y</sub> /TiN produced by magnetron sputtering. Russian Microelectronics, 2016, 45, no. 6, pp. 396–401.

- 41. Бобылев А.Н., Удовиченко С.Ю., Бусыгин А.Н., Ибрагим А.Х. Увеличение диапазона резистивного переключения мемристора для реализации большего числа синаптических состоя-

- ний в нейропроцессоре. Вестник Тюменского государственного университета. Физико-математическое моделирование. Нефть, газ, энергетика, 2019, 5, № 2, с. 124-136.

- 42. Bobylev A.N., Udovichenko S.Y., Busygin A.N., Ebrahim A.H. The Effect of Aluminum Dopant Amount in Titania Film on the Memristor Electrical Properties. Nano Hybrids and Composites, 2020, 28. pp. 59-64.

- 43. **Alekhin A.P., Chouprik A.A., Gudkova S.A.,** et al. Structural and electrical properties of Ti<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub> thin films grown by atomic layer deposition. Journal of Vacuum Science and Technology B, 2011, 29, 01A302.

- 44. **Peng C.**, **Chang W.**, **Lee Y.**, et al. Improvement of Resistive Switching Stability of HfO<sub>2</sub> Films with Al Doping by Atomic Layer Deposition. Electrochemical and Solid-State Letters, 2012, 15,no. 4, pp. H88-H90.

- 45. Писарев А.Д., Бусыгин А.Н., Бобылев А.Н., Удовиченко С.Ю. Комбинированный мемристорно-диодный кроссбар как основа запоминающего устройства. Вестник Тюменского государственного университета. Физико-математическое моделирование. Нефть, газ, энергетика, 2017, 3, № 4, с. 142–149.

- 46. Maevsky O.V., Pisarev A.D., Busygin A.N., Udovichenko S.Y. Complementary memristor-diode cell for a memory matrix in neuromorphic processor. International journal of nanotechnology, 2018, 15, no. 4/5, pp. 388-393.

- 47. Писарев А.Д., Бусыгин А.Н., Бобылев А.Н., Ибрагим А.Х., Губин А.А., Удовиченко С.Ю. Выбор материалов и нанотехнология изготовления комбинированного мемристорного-диодного кроссбара. Основы аппаратной реализации нейропроцессора. Вестник Тюменского государственного университета. Физико-математическое моделирование. Нефть, газ, энергетика, 2019, 5, № 4, с. 200-219.

- 48. **Pisarev A.**, **Busygin A.**, **Bobylev A.**, **Gubin A.**, **Udovichenko S.** Fabrication technology and electrophysical properties of a composite memristor-diode crossbar used as a basis for hardware implementation of a biomorphic neuroprocessor. Microelectronic Engineering, 2021, V.236, 111471.

- 49. Lee M., Park Y., Kang B., et al. 2-stack ID-IR Cross-point Structure with Oxide Diodes as Switch Elements for High Density Resistance RAM Applications. IEEE International Electron Devices Meeting. Washington, DC, USA, 2007, pp. 771–774.